Physical Design or PnR (Place and Route) is the core of any IC design cycle. From a RTL netlist to final tape-out, each phase of PnR brings it’s own challenges and surprises. “What are these challenges?” “What is the process?” “Can I build a chip of my own?”- If you have these questions and if you are eager to delve into the world of ASIC design flow… Wait no more!

With the announcement of Google-SkyWater’s first manufacturable open source 130nm process design kit (pdk), open source EDA world is no longer limited in scope to academic research and small scale projects only. This along with the conception of Openlane flow, a fully-automated RTL2GDSII flow, has made the dream of “an IC for all” a near reality.

So here’s announcing the ultimate workshop on SoC design planning in Openlane flow using the latest Google-SkyWater 130nm process node.

Kunal Ghosh, the visionary co-founder of VLSI System Design (VSD) Corp. Pvt. Ltd., stands at the forefront of online open-source EDA and hardware design education, particularly in the realm of RISC-V.

With a portfolio of 50 top-tier VLSI online courses, Kunal has enriched the learning journey of over 90,000 students across 153 countries. His expertise extends beyond training; he’s actively involved in pioneering open-source projects and design collaborations with esteemed institutions like IIT Madras, IIT Bombay, IIT Guwahati and IIT Hyderabad.

His current focus is on crafting high-quality open-source Analog/Digital IPs, a groundbreaking endeavor in open-source hardware design. Kunal’s rich industry experience includes roles at Qualcomm and Cadence, specializing in SoC design. He holds a master’s degree from IIT Bombay, where he specialized in VLSI & Nano-electronics, with a focus on sub-100nm Electron Beam Lithography Optimization techniques.

Timothy Edwards, Founder Opencircuitdesign.com and SVP at Efabless.He is Analog VLSI designer and collecting and developing open-source EDA tools for over 27 years, He worked for the Johns Hopkins Applied Physics Lab, startups MultiGiG and Analog Devices. He has developed open-source EDA software tools such as Magic, Qflow, Netgen, and Xcircuit.

Mohammed Shalan, Associate Professor, American University in Cairo.He is Founder of CloudV.io, The Open Cloud-based Digital ASIC/FPGA Design Environment, Fault, the only open-source DFT solution. He worked as Embedded Systems Architect for Automotive and Mobile (Mentor Graphics), Embedded Software Manager (MindSpeed and Mentor Graphics), Digital ASIC Designer (Freescale), SoC Consultant, Digital ASIC PnR Consultant.He holds Patents- Power Profiling for Embedded System Design, Power System Optimization and Verification for Embedded System Design.

Ahmed Ghazy, fresh Computer Engineering graduate from the American University in Cairo with a minor in Mathematics. Currently working at eFabless where he worked on the OpenLANE flow 1 for over a year now and made many contributions to open-source EDA tools including the OpenROAD tools, magic, and netgen.Other research interests include computer security and cryptography, data structures and algorithms, and combinatorics.

It's discounted to $30 ($70) as we want everyone to have access to Open-source EDA tools and PDK's for college projects, PhD, Semester Lectures and latest industry trends.

Yes. The workshop is conducted on VSD-IAT cloud platform, which allows you to login at your convenient time within 24hrs from 9th Aug, 00:00hrs IST to 13th Aug, 11:59pm IST.

In our last RISC-V workshop, we had students as young as 8th Grade. So as long as you are looking forward to learning something new and making a bright career in the field of VLSI, you are welcome. This workshop, though it's called advanced, is kept at a very very basic level, where we make sure basics are covered first. Look at curriculum in above registration link.

We would suggest you to refrain from joining this workshop, as it's especially designed only for freshers looking to start in the field of VLSI. But, if you are looking to share your SoC and Physical Design experience with students, then you are more than welcome to join.

You will be given lifetime access to all lab files after the workshop. Access to videos and VSD-IAT platform will terminate on last day of Workshop.

No. Labs will be done on VSD-IAT cloud platform. You will be given access to a Linux Terminal, which has all necessary tools installed. Post workshop, we will provide scripts to install all tools on your laptops so you can do all experiments on your laptop and revise

The labs will be shared through a virtual box image. Detailed steps on how to access and utilize the virtual box image will be provided one day prior to the start of the workshop.

The lectures for the workshop will be delivered via the VSD-IAT LMS platform. Participants will have access to the necessary course materials and can engage with the content at their own pace.

Yes, instructors and Teaching Assistants (TAs) will be available on Slack 24/7 throughout the entire duration of the 5-day workshop. Participants can ask questions, seek clarification, and receive assistance as needed.

Yes, there will be a one-hour sync-up call held daily during the workshop. This call provides an opportunity for participants to address any pressing issues, discuss challenges, and receive immediate guidance and support from the instructors and TAs.

Yes, the workshop is conducted on a cloud-based platform. Participants can log in at their convenient time, complete the lectures and labs for the day, and then log out. This allows flexibility in accessing the workshop materials and completing the required tasks based on individual schedules.

IP Name – 130nm PLL Clock Multiplier IP

8x PLL Clock Multiplier IP on the Google-Skywater 130nm node.

Tested through spice simulations on skywater 130nm tt corner at room termperature

Generates 8x Multiplied Clock.

If you are not able to join workshop, Last date to apply for refund is 8th May 2025 11:59 PM IST.

Fresher or recently graduated or experienced professionals looking to brush fundamentals.

Atleast BE/BTech/ME/MTech or equivalent.

VSD, standing as a trailblazing Semiconductor EdTech company and a community-based Technology Aggregator, is revolutionizing the landscape of VLSI Design. With the belief that “Creativity is just connecting things”, VSD has mastered the art of linking the right resources with the community. This unique approach has sparked a significant transformation in the VLSI Design process.

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Job Roles, Convergence With Embedded Systems, and Startups

VSD showcased at Semicon India 2023

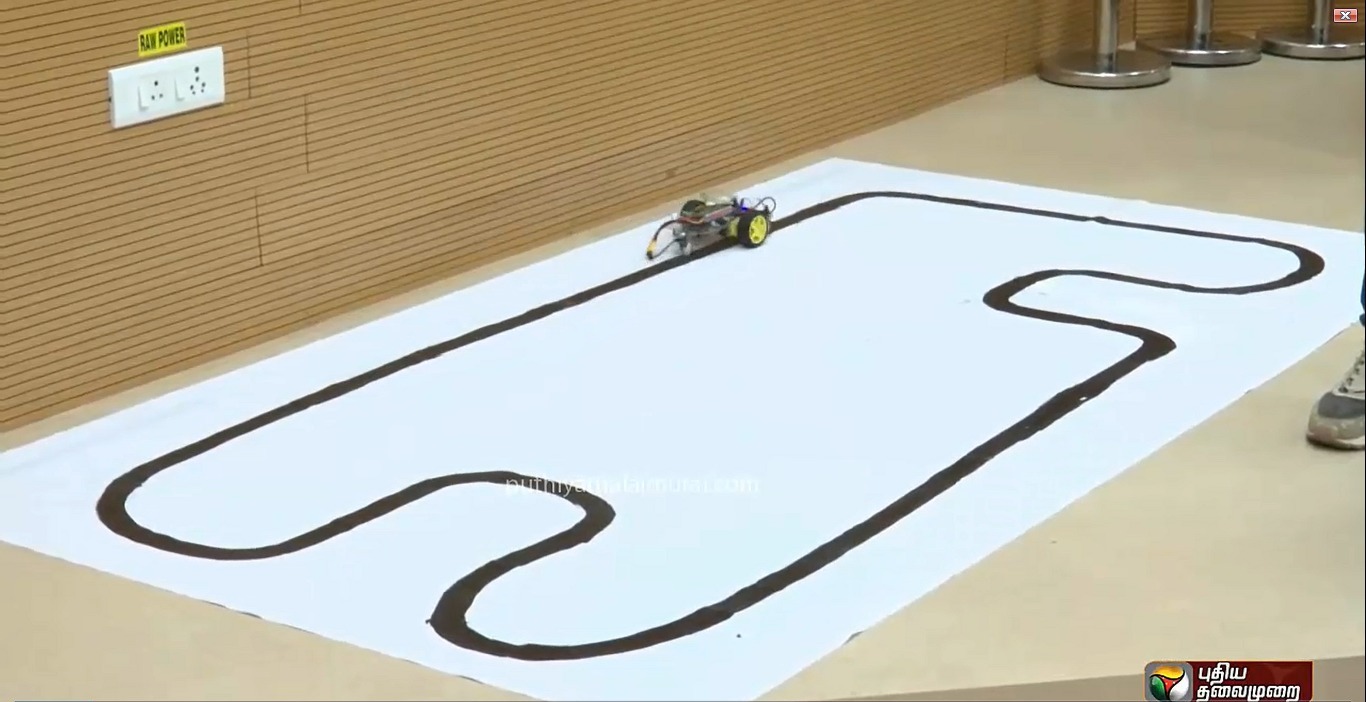

VSDSquadron Educational board on Tamil News channel

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Karnataka VLSI roadshow at Sahyadri College, Mangalore

Welcome to Ethical RISC-V IoT Workshop

The “Ethical RISC-V IoT Workshop” at IIIT Bangalore, organized in collaboration with VSD, is a structured, educational competition aimed at exploring real-world challenges in IoT and embedded systems. Participants progress through three stages: building an application, injecting and managing faults, and enhancing application security. The event spans from May 9 to June 15, 2024, culminating in a showcase of top innovations and an award ceremony. This hands-on hackathon emphasizes learning, testing, and securing applications in a collaborative and competitive environment.

VSDSquadron, a cutting-edge development board based on the RISC-V architecture that is fully open-source. This board presents an exceptional opportunity for individuals to learn about RISC-V and VLSI chip design utilizing only open-source tools, starting from the RTL and extending all the way to the GDSII. The possibilities for learning and advancement with this technology are limitless.

Furthermore, the RISC-V chips on these boards should be open for VLSI chip design learning, allowing you to explore PNR, standard cells, and layout design. And guess what? vsdsquadron is the perfect solution for all your needs! With its comprehensive documentation and scalable labs, thousands of students can learn and grow together.

With VSD Hardware Design Program (VSD-HDP), you have the opportunity to push the boundaries of what exist in open source and establish the new benchmark for tomorrow.

It will leverage your degree in Electrical or Computer Engineering to work with

Sounds exciting to just get started with expert mentors, doesn’t it? But we are looking for the next generation of learners, inventors, rebels, risk takers, and pioneers.

“Spend your summer working in the future !!”

Outcomes of VSD Online Research IP Design Internship Program

VSD – Intelligent Assessment Technology (VSD-IAT) is expertly built training platform and is suited for designer requirements. Semiconductor companies understand the value of training automation and Engineer performance enhancement, and do not need to be convinced of the impact of a virtual platform for learning. VSD trainings are quick, relevant, and easy to access from any device at any time zone.

VSD is working towards creating innovative talent pool who are ready to develop design and products for the new tech world. VSD believes in “Learning by doing principle” , and always prepare the student to apply the knowledge learned in the workshops, webinars and courses. We always push our students to work on new designs, test it and work continuously till it becomes the best performing design. Any student who enrolls to VSD community starts working with small design and grows with us and develops a tapeout level design with complete honesty and dedication towards the Work !!

Check out VSD Interns Achievement!

Welcome to the World’s only online conference in Semiconductor Industry VSDOpen Conference. With enormous support and global presence of audience from different segments of industrial lobby and academia made a highly successful event. Evolution is change in the genetic makeup of a population over time, online conference is one kind evaluation everyone adapt soon.

VSD offers online course in complete spectrum of vlsi backend flow from RTL design, synthesis and Verification, SoC planning and design, Sign-off analysis, IP Design, CAD/EDA automation and basic UNIX/IT, Introduction to latest technology – RISC-V, Machine intelligence in EDA/CAD, VLSI Interview FAQ’s.

Current Reach – As of 2021, VSD and its partners have released 41 online VLSI courses and was successfully able to teach ~35900 Unique students around 151 countries in 47 different languages, through its unique info-graphical and technology mediated learning methods.