Hello

….continuing from Part1 and Part2

After the terrible layout we saw in last 2 blogs, without considering euler’s path, its now time to mend things and do it the right way, i.e. create an accurate gate input ordering using euler’s path, extracting stick diagram and finally drawing the layout.

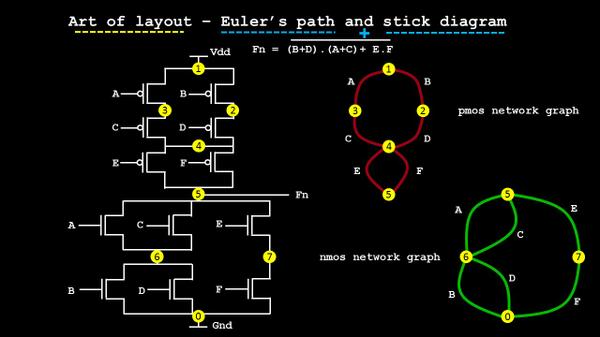

Let’s first create the below pmos and nmos network graph using transistors gate inputs as ‘edges’. (to learn more about euler’s path, euler’s circuit and stick diagram, visit this link)

The node number 1, 2, 3, 4…etc. which you see encircled with yellow are called vertices and the gate inputs which labels the connections between the vertices 1, 2, 3, 4,…etc are called edges. Find out more about vertices and edges in this link

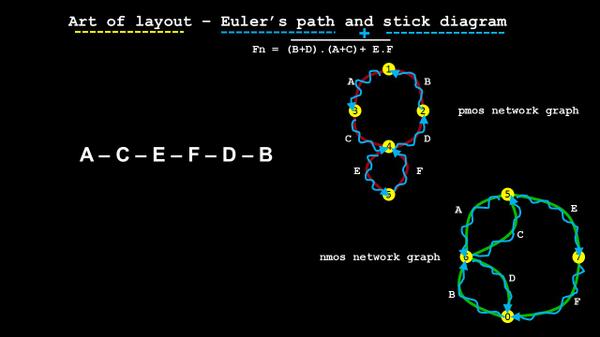

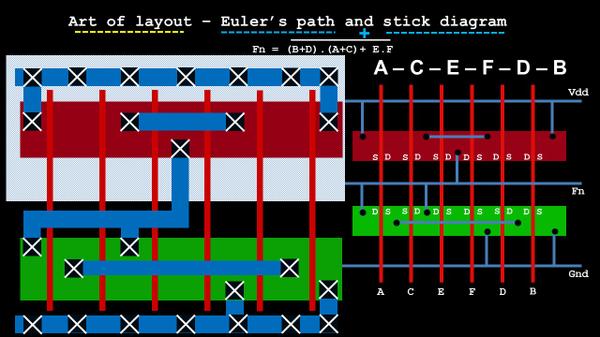

Next, we trace a path in both nmos and pmos network, in such a fashion that each edge is traversed only once. While we do that, we keep on registering the edge (or the gate input) we are travelling. I do that and I get the below euler’s path i.e. A-C-E-F-D-B

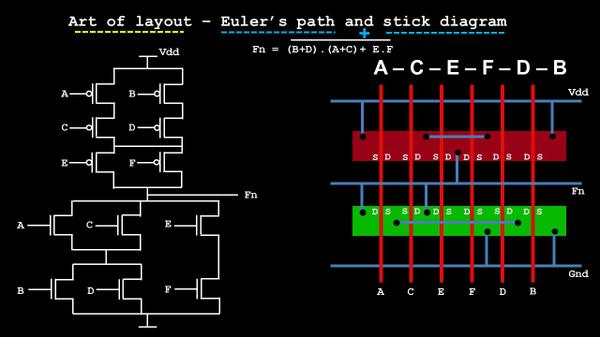

Do you wanna see the power of euler’s path? See the below layout implementing the same circuit, but in a much simpler fashion as compared to one which we did in our previous post

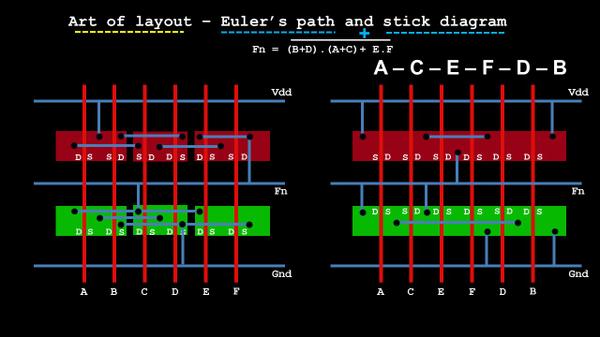

Now compare this with previous layout below. Doesn’t this look much cleaner, much organized and much simpler to implement in a layout editor? It does look…

Once done with stick diagram, the last step is the most easy one. i.e build the layout along with dimensions pertaining to design rules and below is what you get:

Wasn’t that a smartest way to implement layout? And I guarantee you, you take the toughest design, break into smaller logic, build each logic using euler’s path and stick diagram, and connect each layout back….you will get the most optimized layout in terms of area and power. Guess what you need to do to increase the performance….just increase width of p-diff/n-diff and make it low resistance path to VDD and GND… This is what my STA friends call as ‘sizing’..

How cool is that? Your STA is somehow related to the concepts about euler’s path and stick diagram we just talked about in above and previous 2 blogs ….

And as Alvin Toffler very rightly said : “You’ve got to think about big things while you’re doing small things, so that all small things go in right direction“

So think big …. and take small steps to achieve it….

Till then … happy learning ….