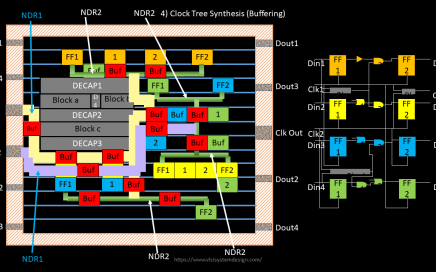

Selective Non-Default Rules Based Clock Tree Synthesis using open-source EDA

Hey There – Think about it…!! Problem Statement – For hierarchical designs ~500k instance count, participants are expected to develop code which will modify existing […]

Hey There – Think about it…!! Problem Statement – For hierarchical designs ~500k instance count, participants are expected to develop code which will modify existing […]

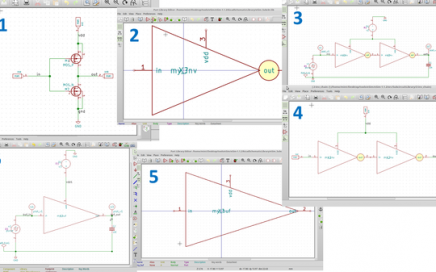

….And this is something which I can show you using the newly launched open-source EDA tool “eSim (FOSSEE IITB Project)”. Let’s assume for a moment, […]

Hello We were looking for a solution for below scenario, and you will be amazed to see, how an ‘Universal Gate’ solves the below problem […]

Hello And here’s the solution to the problem posted in my previous article. ‘AND gate itself’. If you observe carefully, you tie one of the […]

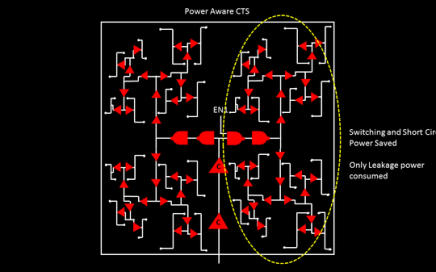

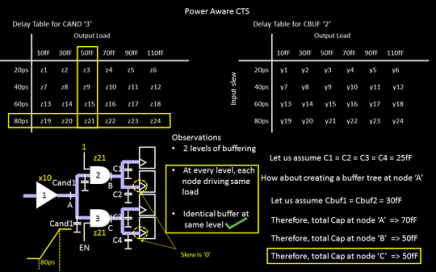

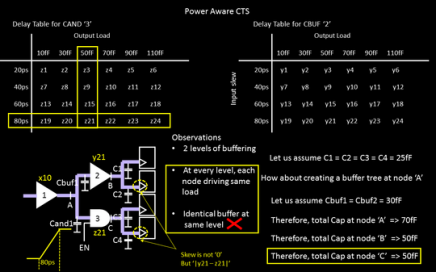

Hello While trying to build a clock tree which is power aware, let’s go back a step ahead and look, what are the top observations […]