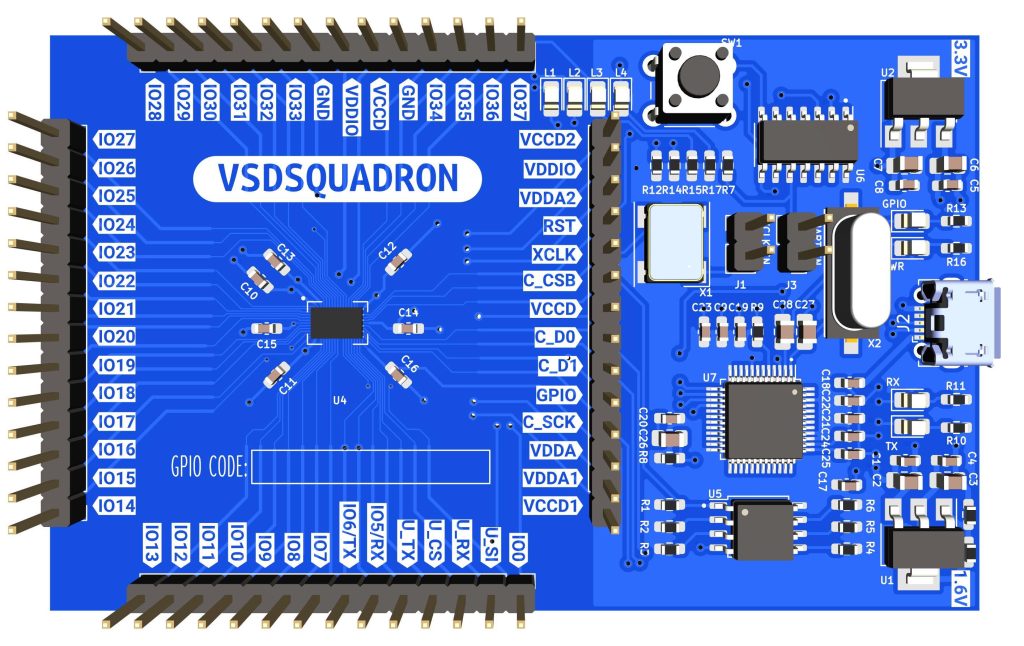

While you could do an embedded system design course using “vsdsquadron”, but you could do a lot more as “vsdsquadron” is built for chip designers. With a comprehensive curriculum covering topics such as RISC-V ISA, digital logic design, PCB design, and more, learners can gain a solid foundation in electronics system design and chip design. Additionally, the availability of opensource simulation tools, PDKs and verification resources ensures that learners can explore these subjects in-depth and develop a deeper understanding of the concepts.

There are a bunch of topics, infact an entire chip design curriculum which you can learn using “vsdsquadron”, but let me give you a quick summary of topics which you can cover using “vsdsquadron”

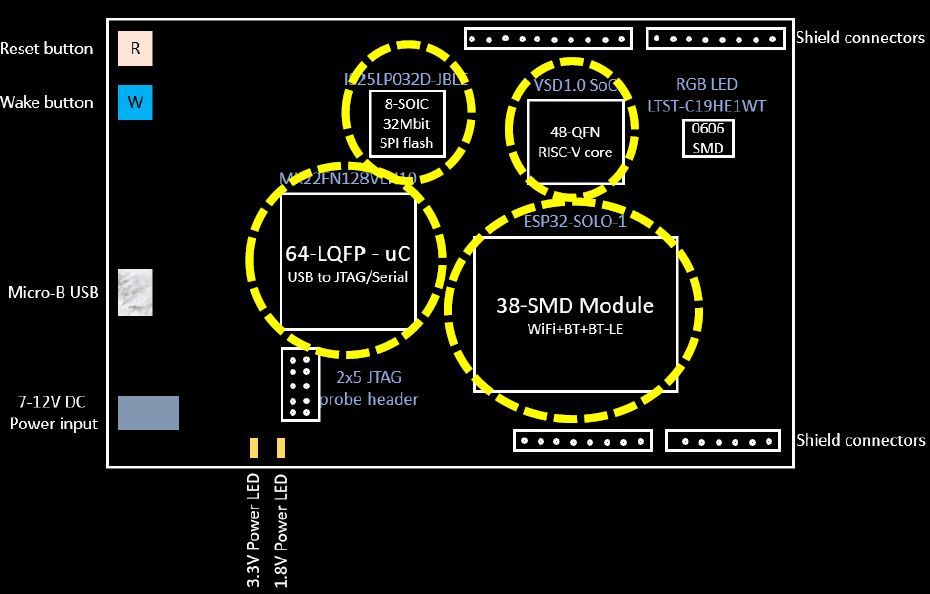

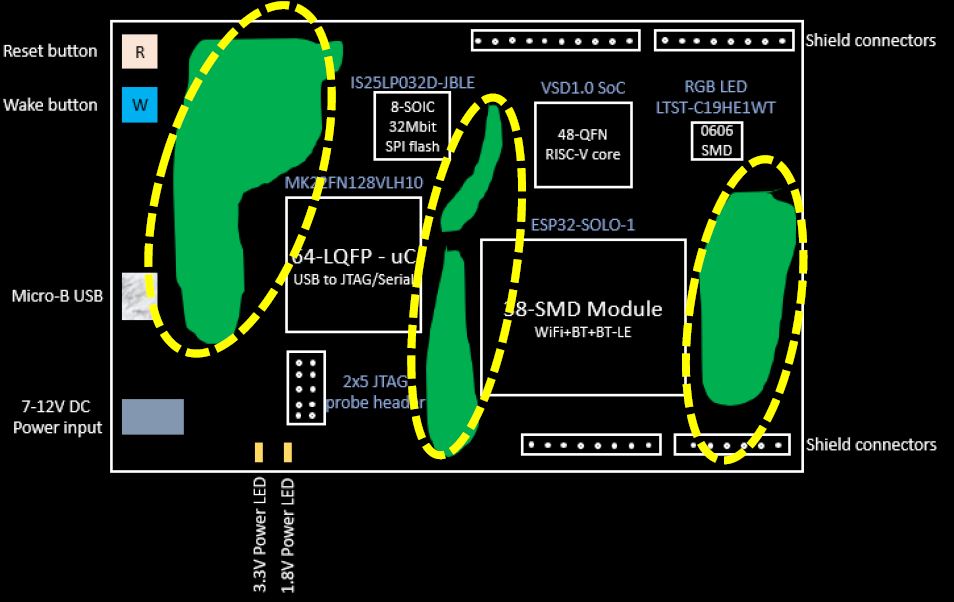

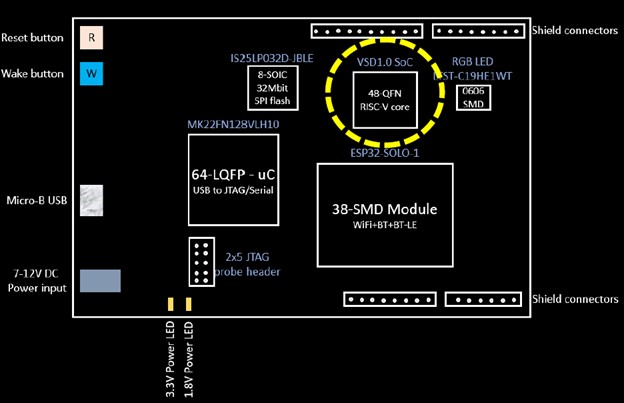

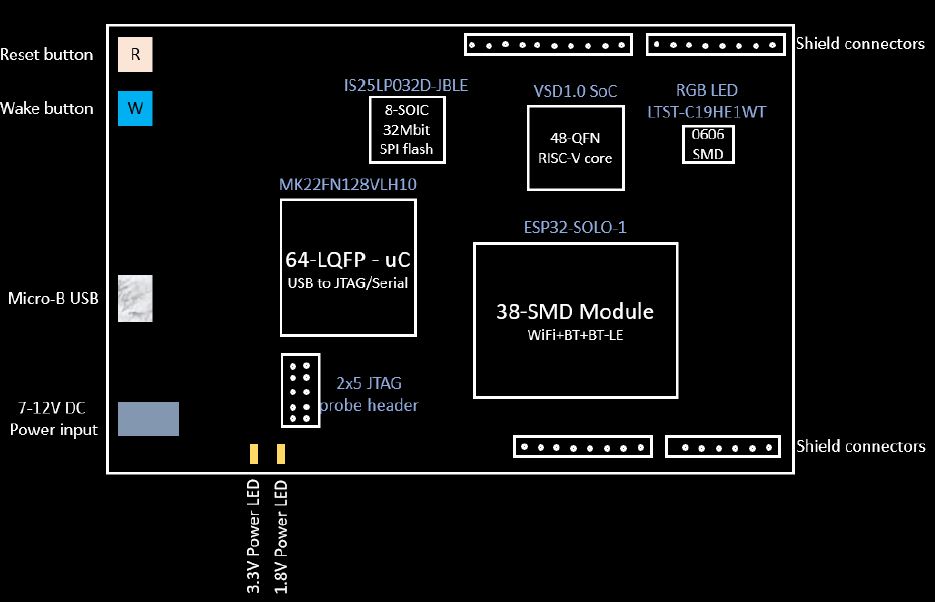

Topic 1 - Development Kit specification design

The Development Kit specification design covers several topics related to the design of a development board. It includes the system hardware specifications necessary for real-time applications, the system architecture, block diagrams, and data flow. Additionally, it explains the need for specific components such as a RISC-V chip, WiFi+BT module, K20 uC, 32MBIT flash, and a supervisor circuit. The document also outlines the board design flow, from initial specification to final PCB layout. Overall, the specification design aims to provide a comprehensive guide for designing a development kit that meets the requirements of real-time applications.

Topic 2 - Discrete Devices – Resistors, Capacitors, Diodes (TVS, LED), Connectors, Transistors, Switches, Regulators, Oscillators and Crystal

The Discrete Devices document covers a variety of electronic components, including ceramic capacitors, MLCC capacitors, resistors, ESD suppressors/TVS diodes, diodes, LEDs, connectors (header, USB, power barrel), transistors, switches, regulators, oscillators, and crystals. The document provides detailed information on the specifications and characteristics of each component, including their voltage and current ratings, package sizes, and application areas. The variety of discrete components covered in the document reflects their importance in building complex electronic systems and highlights the need for engineers and designers to have access to a wide range of components to create custom electronic solutions.

Topic 3 - PCB Power supply design and Interfaces in schematics

The PCB Power Supply Design and Interfaces in Schematics document covers a range of topics related to power supply design and interface circuitry in electronic systems. The document highlights the importance of power supply design and the use of ferrite beads for filtering circuitry to prevent electromagnetic interference (EMI) in the system. It also discusses power sequencing and the use of multiple power supplies, as well as the importance of LDOs and DC/DC converters in voltage regulation. The document also covers the need for pullup/pulldown series resistors and decoupling capacitors, differential/single-ended signals, capacitors for crystal, reset circuits, protection diodes, DDR4 interfaces, level translators, USB connectors, and Ethernet interfaces. Overall, the document emphasizes the importance of effective power supply design and interface circuitry for the reliable and efficient operation of electronic systems.

Topic 4 - RISC-V based MYTH (uP for You in Thirty Hours) and RISC-V functional verification

The topics covered in RISC-V based MYTH (uP for You in Thirty Hours) and RISC-V functional verification are: RISC-V ISA, GNU compiler tool-chain and ABI, digital logic design, single-stage and pipelined RISC-V micro-architecture design, directed test-bench, bus functional models, UVM testbench, sequencers, snooper, monitors, memory-mapped (APB/Avalon) and UVM factory, derived sequence items, design arithmetic unit and high-speed adder circuits, pipelining and Wallace tree multiplier, sequential circuits, and cache coherent protocol.

Topic 5 – RISC-V SoC design, CAD for VLSI design, Synthesis, CMOS circuit design and SPICE simulations

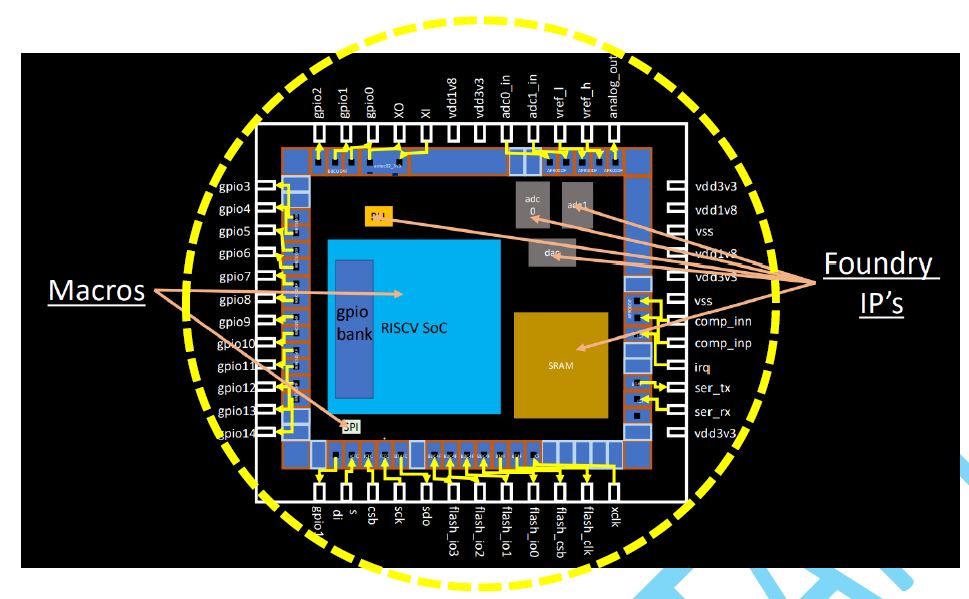

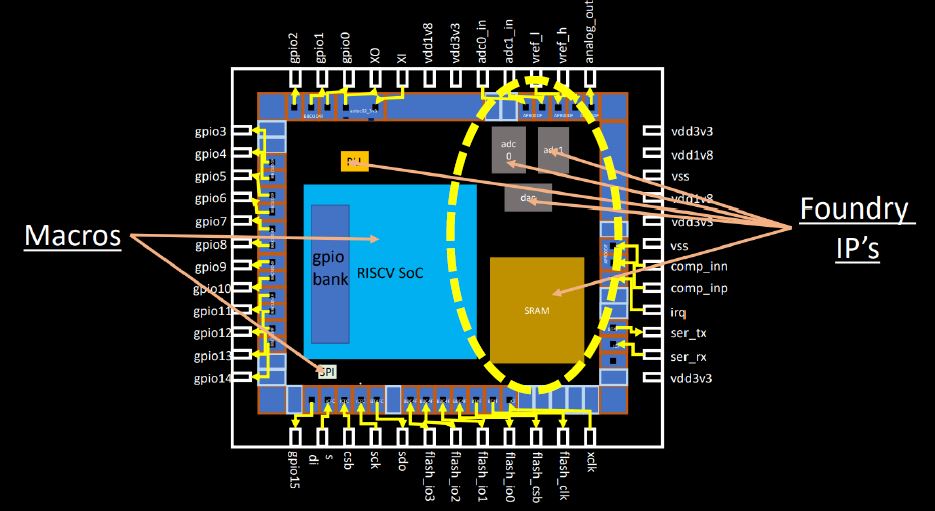

The topics covered in these three courses include RISC-V based SoC design, CAD for VLSI design, CMOS circuit design, SPICE simulations, logic synthesis, and RISC-V physical design. In the RISC-V SoC design course, analog components, analog calibration, SoC memory map, and top-level connections are covered, while the CAD for VLSI design course covers logic synthesis, compilation, translation, and linking, as well as optimization in synthesis. The CMOS circuit design course covers NMOS/PMOS basics, velocity saturation, CMOS VTC, CMOS static/dynamic behavior, and CMOS robustness, along with Threshold voltage Id-Vds and Id-Vgs simulations.

Topic 6 - Analog IP design – Bandgap, PLL, ADC, DAC Comparator, 4kB SRAM

The topics covered in Analog IP Design include Bandgap references, Phase-Locked Loops (PLL), Analog-to-Digital Converters (ADC), Digital-to-Analog Converters (DAC), Comparators, and 4kB Static Random-Access Memory (SRAM). For Bandgap references, the course covers the principles of generation, start-up circuit, PSRR, temperature co-efficient, and design/layout techniques. In PLL, the focus is on clock multiplier, VCO, PFD, charge-pump, frequency divider, and design/layout techniques. The ADC course covers functionality, resolution, INL, DNL, prep time, conversion time, timing diagram, and design/layout techniques. Similarly, the DAC course covers functionality, resolution, accuracy, FSV, 1LSB, and DNL. The Comparator course focuses on functionality, hysteresis, propagation delay, noise requirement, and design/layout techniques. Lastly, the course on 4kB SRAM covers SRAM architecture, 6T memory cell, butterfly curve, sense amplifier, write driver, tri-state buffer, pre-charge circuit, layout, design techniques, and OpenRAM compiler configuration.

Topic 7 - RISC-V SoC Physical design implementation

The RISC-V SoC Physical design implementation covers the process of synthesizing the design using target process and IP's, followed by IO port placement, floorplanning, power planning, and IP placement. The process also includes full-chip integration, place and route (PNR), static timing analysis (STA), design rule check (DRC), and layout versus schematic (LVS) checks. This phase ensures the design meets timing and power constraints and that there are no manufacturing defects in the final layout.

Topic 8 - PCB design

The topics covered in PCB design include component placement, which can have a significant impact on the board's performance, PCB stack-up, which affects EMI/EMC, and routing techniques. Additionally, BOM, Gerber files, and assembly guidelines are covered, which are necessary for manufacturing and assembly. By mastering these skills, designers can create high-quality, reliable PCBs that meet the specifications and requirements of the application.

The VSDSquadron educational board provides a unique opportunity for learners to gain hands-on experience in electronics system design and chip design. The board's open-source nature allows for easy access to IPs, PDKs, and tools, including RISC-V, providing learners with a complete and comprehensive curriculum in these areas. With the board's built-in modules covering a range of topics such as analog IP design, RISC-V SoC design, PCB design, and more, learners can acquire practical skills and knowledge essential for a career in the field. In summary, the VSDSquadron educational board offers a rich and dynamic learning experience in electronics system design and chip design.

International payments are now open. You can pre-order your board using below link

Related Posts:

- Accelerating the Future of Semiconductor Talent with…

- RISC-V Mini Game Console

- Home safety system

- Bluetooth automated smart access

- Water level monitoring and control in water tank

- The Future of Chip Design: The Next Generation is…

- Shape Tomorrow’s Technology Today: ELCIA Hackathon…

- Real Time Implementation of BitNetMCU

- COLORIMETER

- PARKinSENSE