We recently did a webinar on Timing ECO and the main point of discussion was how do you do a power aware ECO. A timing ECO should be power, performance and area aware and that was the crux of this webinar, where we discussed several strategies about how to do effective ECO as an expert

Slack based ECO is a beautiful strategy which helps you to achieve your timing target, while helping you to reduce on power and area

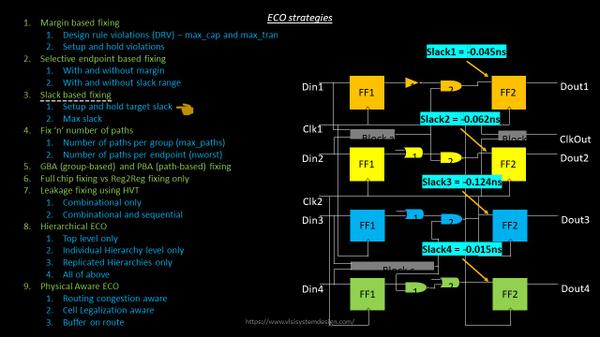

Let’s take an example of below slacks:

Let’s say, we have 4 timing paths. On a real design with 100K flops, the number of timing paths will be approximately 100K. So, any discussion on slack based ECO, should be extrapolated on to real design timing path count to see the impact.

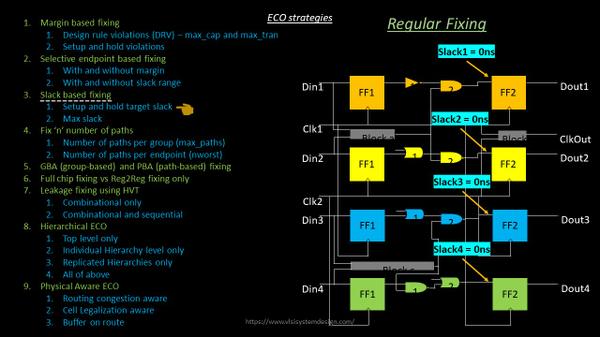

In regular fixing strategy, if you want to fix setup on the above 4 paths, you will upsize cells (power and area impact), and bring down the slack to 0ns as shown below:

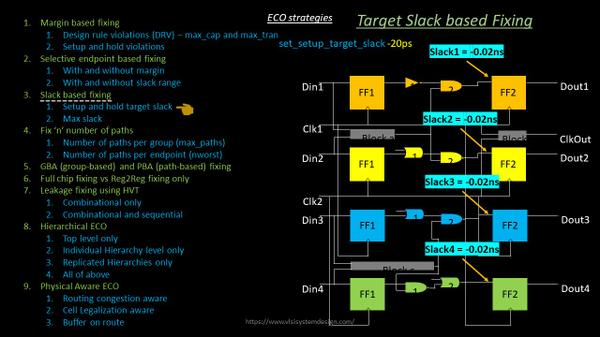

In a slack based fixing, we fix the final slack limit to which you want the timing path to be fixed using upsize cells, and then fix the path only till that slack value. For eg. in below image, let’s say we fix the slack limit as -20ps (or -0.02 ns) using some command say “set_setup_target_slack as -20ps” (this command is invented just was explanation purpose).

Now, all the cells in the above 4 paths, will be upsized to a certain limit to bring down the slack, not to 0ns, but to -20ps. The “-20ps” leftover slack can be hand-fixed or just waived off by looking at PBA slack (path-based analysis slack, again an important topic, discussed in the webinar course). This way, you save lot of area, as very limited cells will be upsized, or cells will be upsized to certain limit.

And since the cells are upsized to a certain limit, the amount of power (short-circuit and leakage mainly) will be restricted or reduced, compared to regular fixing. Isn’t that an optimized way to fix timing paths while still restricting power and area?

There’s a tradeoff between performance and power/area, which brings me to a very important quote:

“Everything is a trade-off. The more you focus on details, the more difficult it is to decipher big ideas to take into your brain bank” – Sandra Bond Chapman

Enroll now and learn more timing ECO strategies …. Happy Learning….