Welcome to the fascinating universe of Hardware Design, where the pulse of every IC design cycle beats. Imagine transforming a bare RTL netlist into a masterpiece of engineering, the final tape-out. Each stage in the PnR process is a new chapter filled with unique challenges and revelations.

Do you find yourself asking, “What are these obstacles?” “How does this intricate process work?” “Could I actually create my own chip?” If these questions ignite your curiosity and you’re passionate about delving into the ASIC design flow, your adventure starts here!

We’re excited to introduce a game-changer: the Google-Sky Water collaboration has unveiled the first open source, manufacturable 130nm process design kit (pdk). This innovation transcends the boundaries of academic research and small-scale projects, propelling the open-source EDA world into a new dimension. Coupled with the inception of Openlane flow, a fully automated RTL2GDSII process, we’re closer than ever to realizing the dream of “an IC for everyone.”

Seize this unparalleled opportunity to transform your passion into expertise!

Here’s a sneak peek at the powerful open-source tools you’ll be mastering, each a key player in the transformative journey of IC design:

Join us as we explore these incredible tools, each a gateway to mastering the art of IC design. This program isn’t just about learning; it’s about transforming knowledge into power, ideas into reality.

Objective:

Get familiar with the environment, tools, and basic RISC-V workflow.

Tasks:

Deliverable:

GitHub repo with snapshots and documentation.

Objective:

Understand the impact of optimization flags in RISC-V.

Tasks:

Deliverable:

GitHub repo with simulation results and detailed observations.

Objective:

Decode and analyze RISC-V instructions.

Tasks:

Deliverable:

Documented 32-bit instruction patterns.

Objective:

Gain experience in Verilog functional simulation.

Tasks:

Deliverable:

Objective:

Implement a pipelined RISC-V processor.

Tasks:

Deliverable:

GitHub repo with design files, documentation, and waveforms.

Objective:

Integrate rvmyth with BabySoC and verify outputs.

Tasks:

Deliverable:

GitHub repo with integrated design and waveform outputs.

Objective:

Perform synthesis and compare functional and synthesized outputs.

Tasks:

Deliverable:

GitHub repo with comparisons and synthesis snapshots.

Objective:

Perform Static Timing Analysis (STA) on RISC-V design.

Tasks:

Deliverable:

GitHub repo with detailed STA analysis and graphs.

Objective:

Understand advanced physical design workflows.

Tasks:

Deliverable:

GitHub repo with detailed OpenLane design analysis and documentation.

Objective:

Perform SoC design implementation using OpenROAD.

Tasks:

Deliverable:

GitHub repo with SoC implementation project files and analysis.

Ensure the GitHub repository is complete with:

Program Week-wise Content Breakdown:

Join us for this transformative journey and turn your fascination into tangible skills in the ever-evolving world of IC design!

We’ve tailored every aspect of the program to ensure an effective and enjoyable learning journey:

Practical Get hands-on experience with our easy-to-access labs, available through a virtual box image. We’ll provide clear, step-by-step instructions to help you set up and make the most of these labs, starting one day before the program kicks off.

Discover the intricacies of Physical Design with our comprehensive lectures, hosted on the VSD-IAT LMS platform. This intuitive platform not only gives you access to all necessary course materials but also allows you to explore the content at a pace that suits you.

Have questions or need clarifications? Our team of instructors and Teaching Assistants (TAs) are available 24/7 on Slack during the 5-day program. We’re here to assist you whenever you need it, ensuring a smooth learning experience.

Join us for a daily one-hour call, a perfect opportunity to address any immediate concerns, discuss challenges, and get direct guidance from our instructors and TAs. These calls are designed to keep you connected and supported throughout your learning journey.

Kunal Ghosh, the visionary co-founder of VLSI System Design (VSD) Corp. Pvt. Ltd., stands at the forefront of online open-source EDA and hardware design education, particularly in the realm of RISC-V.

With a portfolio of 50 top-tier VLSI online courses, Kunal has enriched the learning journey of over 90,000 students across 153 countries. His expertise extends beyond training; he’s actively involved in pioneering open-source projects and design collaborations with esteemed institutions like IIT Madras, IIT Bombay, IIT Guwahati and IIT Hyderabad.

His current focus is on crafting high-quality open-source Analog/Digital IPs, a groundbreaking endeavor in open-source hardware design. Kunal’s rich industry experience includes roles at Qualcomm and Cadence, specializing in SoC design. He holds a master’s degree from IIT Bombay, where he specialized in VLSI & Nano-electronics, with a focus on sub-100nm Electron Beam Lithography Optimization techniques.

Timothy Edwards, the mastermind behind Opencircuitdesign.com and the Senior Vice President at Efabless, is a seasoned Analog VLSI designer with over 32 years of dedication to developing open-source EDA tools. His career journey has taken him through notable organizations such as Johns Hopkins Applied Physics Lab, startups MultiGiG, and Analog Devices. Timothy is the brain behind renowned open-source EDA software tools like Magic, Qflow, Netgen, and Xcircuit.

Professor Mohammed Shalan of the American University in Cairo is not only an academic but also a trailblazer in the field of digital ASIC/FPGA design, evidenced by his founding of CloudV.io and Fault. His professional repertoire includes roles in embedded systems architecture for the automotive and mobile sectors at Mentor Graphics, as well as positions at MindSpeed, Freescale, and as a SoC consultant. Mohammed is a patent holder in Power Profiling and Optimization for Embedded System Design.

We’ve set a special discounted fee of $450 ($999). Our aim is to make Open-source EDA tools and PDKs accessible for various purposes such as college projects, PhD research, semester lectures, and keeping up with industry trends.

Absolutely! The program is hosted on the VSD-IAT cloud platform, offering flexibility to log in at your convenience. The platform is accessible 24 hours a day during the ten weeks duration of the program.

Definitely! We welcome learners of all ages and backgrounds. Our previous RISC-V program included students as young as those in 8th grade. This program, while advanced in title, starts with the basics to ensure a solid foundational understanding.

This program is primarily designed for newcomers to the field of VLSI. However, experienced professionals interested in sharing their expertise with students are more than welcome to join.

Yes, you will receive lifetime access to all lab files. However, access to the videos and the VSD-IAT platform will end with the program.

No, all labs will be conducted on the VSD-IAT cloud platform using a Linux Terminal with all necessary tools pre-installed. Post-program, we will provide scripts for you to install these tools on your own computer for further practice and revision.

Labs will be shared via a virtual box image. You’ll receive detailed instructions on accessing and using this image a day before the program starts.

Lectures will be delivered through the VSD-IAT LMS platform. This platform allows you to access course materials and interact with the content at your own pace.

Yes, our instructors and Teaching Assistants are available 24/7 on Slack throughout the 10 week program to answer questions, provide clarifications, and help.

Indeed, there’s a daily one-hour sync-up call during the program. This is a valuable time for discussing any immediate issues, challenges, and for receiving direct guidance from instructors and TAs.

Yes, the program is hosted on a cloud-based platform, allowing you to access materials and complete tasks at your convenience, ensuring flexibility in your learning schedule.

If you are not available to attend the program, Raise refund request before the last day of registration date in Indian Standard Time zone for the training/workshop/design program.

Last date to raise refund request– (2 Nov 2024 11:59 PM IST)

All refunds will be processed within 10 working days after the refund request is approved by VSD.

Please read Terms and Condition Policy : https://www.vlsisystemdesign.com/terms-and-conditions/

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Job Roles, Convergence With Embedded Systems, and Startups

VSD showcased at Semicon India 2023

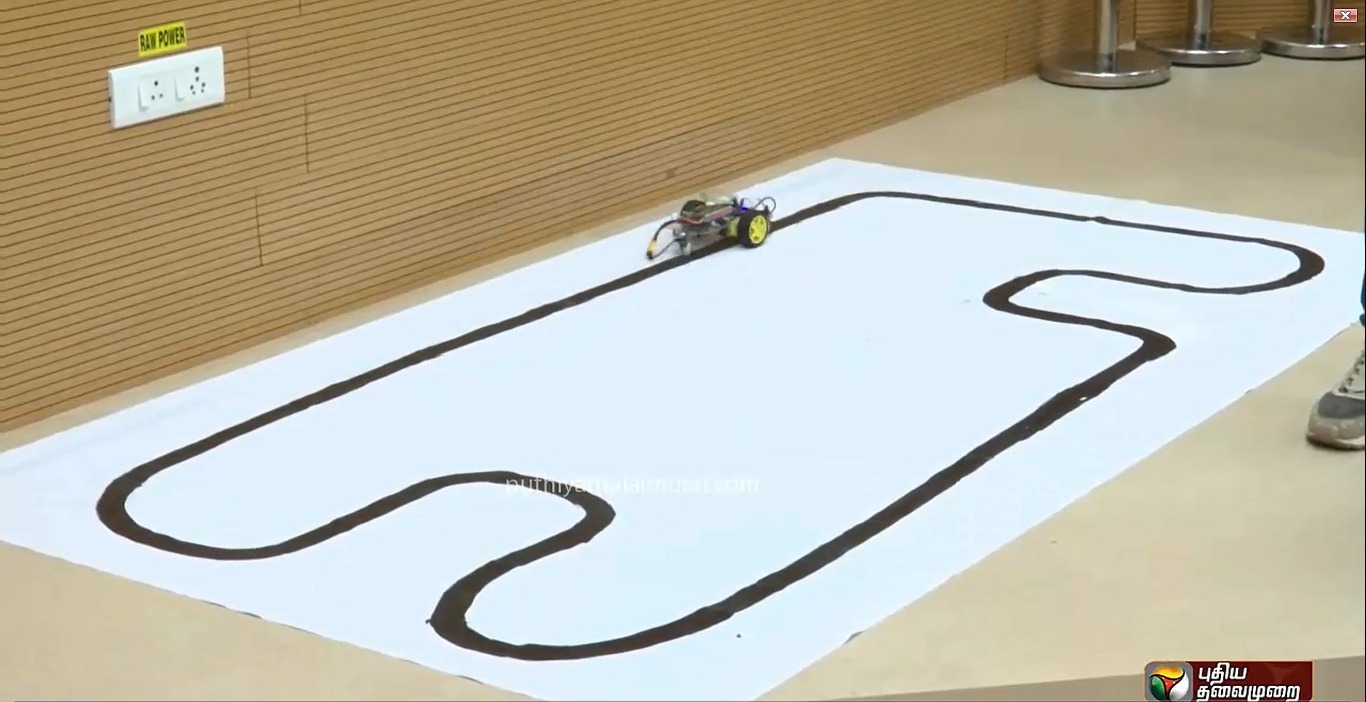

VSDSquadron Educational board on Tamil News channel

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Karnataka VLSI roadshow at Sahyadri College, Mangalore

Welcome to Ethical RISC-V IoT Workshop

The “Ethical RISC-V IoT Workshop” at IIIT Bangalore, organized in collaboration with VSD, is a structured, educational competition aimed at exploring real-world challenges in IoT and embedded systems. Participants progress through three stages: building an application, injecting and managing faults, and enhancing application security. The event spans from May 9 to June 15, 2024, culminating in a showcase of top innovations and an award ceremony. This hands-on hackathon emphasizes learning, testing, and securing applications in a collaborative and competitive environment.

VSDSquadron, a cutting-edge development board based on the RISC-V architecture that is fully open-source. This board presents an exceptional opportunity for individuals to learn about RISC-V and VLSI chip design utilizing only open-source tools, starting from the RTL and extending all the way to the GDSII. The possibilities for learning and advancement with this technology are limitless.

Furthermore, the RISC-V chips on these boards should be open for VLSI chip design learning, allowing you to explore PNR, standard cells, and layout design. And guess what? vsdsquadron is the perfect solution for all your needs! With its comprehensive documentation and scalable labs, thousands of students can learn and grow together.

With VSD Hardware Design Program (VSD-HDP), you have the opportunity to push the boundaries of what exist in open source and establish the new benchmark for tomorrow.

It will leverage your degree in Electrical or Computer Engineering to work with

Sounds exciting to just get started with expert mentors, doesn’t it? But we are looking for the next generation of learners, inventors, rebels, risk takers, and pioneers.

“Spend your summer working in the future !!”

Outcomes of VSD Online Research IP Design Internship Program

VSD – Intelligent Assessment Technology (VSD-IAT) is expertly built training platform and is suited for designer requirements. Semiconductor companies understand the value of training automation and Engineer performance enhancement, and do not need to be convinced of the impact of a virtual platform for learning. VSD trainings are quick, relevant, and easy to access from any device at any time zone.

VSD is working towards creating innovative talent pool who are ready to develop design and products for the new tech world. VSD believes in “Learning by doing principle” , and always prepare the student to apply the knowledge learned in the workshops, webinars and courses. We always push our students to work on new designs, test it and work continuously till it becomes the best performing design. Any student who enrolls to VSD community starts working with small design and grows with us and develops a tapeout level design with complete honesty and dedication towards the Work !!

Check out VSD Interns Achievement!

Welcome to the World’s only online conference in Semiconductor Industry VSDOpen Conference. With enormous support and global presence of audience from different segments of industrial lobby and academia made a highly successful event. Evolution is change in the genetic makeup of a population over time, online conference is one kind evaluation everyone adapt soon.

VSD offers online course in complete spectrum of vlsi backend flow from RTL design, synthesis and Verification, SoC planning and design, Sign-off analysis, IP Design, CAD/EDA automation and basic UNIX/IT, Introduction to latest technology – RISC-V, Machine intelligence in EDA/CAD, VLSI Interview FAQ’s.

Current Reach – As of 2021, VSD and its partners have released 41 online VLSI courses and was successfully able to teach ~35900 Unique students around 151 countries in 47 different languages, through its unique info-graphical and technology mediated learning methods.