# VLSI System Design (VSD)

# VSDSquadron FM (FPGA Mini)

The VSDSquadron FPGA Mini (FM) board is a compact, low-cost prototyping solution with an on-board FPGA programmer, flash, LED, and all FPGA pins easily accessible for seamless development

## Contents

| 1                           | Getting Started  |                                                                               |    |

|-----------------------------|------------------|-------------------------------------------------------------------------------|----|

|                             | 1.1              | Kit Contents                                                                  | 4  |

|                             | 1.2              | Block Diagram                                                                 | 5  |

|                             | 1.3              | Web Resources                                                                 | 5  |

|                             | 1.4              | Board Overview                                                                | 5  |

|                             |                  | 1.4.1 Form Factor                                                             | 6  |

|                             |                  | 1.4.2 Table 2 shows ICE40UP5K-SG48ITR FPGA device IO Bank Assignment for      |    |

|                             |                  | communication Interfaces                                                      | 8  |

|                             |                  | 1.4.3 The following table 3 lists the important components of the VSDSquadron |    |

|                             |                  | FPGA Mini (FM) board                                                          | 8  |

|                             | 1.5              | Handling the Board                                                            | 8  |

|                             | 1.6              | Operating Temperature                                                         | 8  |

|                             | 1.7              | Powering Up the Board                                                         | 8  |

| 2 Installation and Settings |                  |                                                                               | 10 |

|                             | 2.1              | Installation Instructions for Windows Users                                   | 10 |

| 3 Board Component Placement |                  |                                                                               |    |

|                             | 3.1              | VSDSquadron FM top view                                                       | 19 |

|                             | 3.2              | VSDSquadron FM bottom view                                                    | 19 |

| 4                           | Revision History |                                                                               | 20 |

| 5                           | Help and support |                                                                               |    |

# List of Tables

| 1 | Kit Contents                                     | 4 |

|---|--------------------------------------------------|---|

|   | ICE40UP5K-SG48ITR FPGA device IO Bank Assignment |   |

| 3 | ICE40UP5K-SG48ITR FPGA Specifications            | 8 |

| 4 | Revision History                                 | ( |

# List of Figures

| 1        | VSDSquadron FPGA Mini (FM) board Block Diagram |

|----------|------------------------------------------------|

| <b>2</b> | VSDSquadron FPGA Mini (FM) board               |

| 3        | Micro-C end of USB cable connected to board    |

| 4        | Diskspace check                                |

| 5        | Virtual Machine Launch                         |

| 6        | Allocate RAM and Number of CPUs                |

| 7        | Choose VSDSquadron FPGA Mini VDI               |

| 8        | Finish Setup                                   |

| 9        | Start virtual machine                          |

| 10       | Enter Password                                 |

| 11       | Steps to Open Terminal                         |

| 12       | View Terminal                                  |

| 13       | Navigate through project directory             |

| 14       | Connecting the Board to USB                    |

| 15       | FTDI Message from 'lsusb' Command              |

| 16       | Output Screen after 'make clean' command       |

| 17       | Output Screen after 'make build' command       |

| 18       | Output Screen after Flashing the Code          |

| 19       | Silkscreen Top View                            |

| 20       | Silkscreen Top View                            |

### 1 Getting Started

The VSDSquadron FM board - Features and specifications:

#### • FPGA:

- Powered by the Lattice UltraPlus ICE40UP5K FPGA

- Offers 5.3K LUTs, 1Mb SPRAM, 120Kb DPRAM, and 8 multipliers for versatile design capabilities

#### • Connectivity:

- Equipped with an FTDI FT232H USB to SPI device for seamless communication

- All FTDI pins are accessible through test points for easy debugging and customization

### • General Purpose I/O (GPIO):

- All 32 FPGA GPIOs brought out for easy prototyping and interfacing

#### • Memory:

- Integrated 4MB SPI flash for data storage and configuration

#### • LED Indicators:

- RGB LED included for status indication or user-defined functionality

#### • Form Factor:

Compact design with all pins accessible, perfect for fast prototyping and embedded applications

The VSDSquadron FPGA Mini (FM) board is an affordable, compact tool for prototyping and embedded system development. With powerful ICE40UP5K FPGA, onboard programming, versatile GPIO access, SPI flash, and integrated power regulation, it enables efficient design, testing, and deployment, making it ideal for developers, hobbyists, and educators exploring FPGA applications.

#### 1.1 Kit Contents

The following table number 1 lists the contents of the VSDSquadron FPGA Mini (FM) board.

| Item |                                                                   | Quantity |

|------|-------------------------------------------------------------------|----------|

|      | M) board with Lattice ICE40UP5K and onboard power for prototyping | 1        |

Table 1: Kit Contents

#### 1.2 Block Diagram

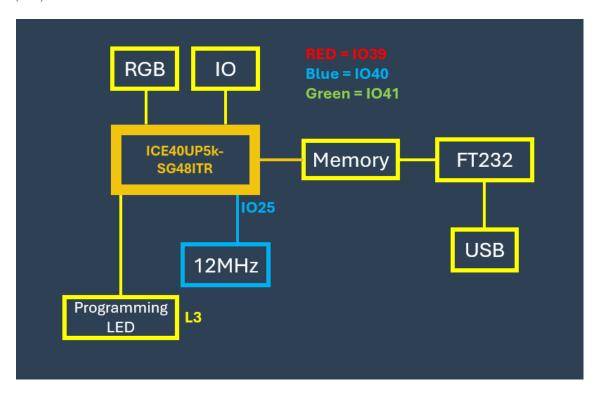

The block diagram shown in Figure 1 shows the key components of the VSDSquadron FPGA Mini (FM) board.

Figure 1: VSDSquadron FPGA Mini (FM) board Block Diagram

#### 1.3 Web Resources

For more information about the VSDS quadron FPGA Mini (FM) device, refer to ICE40UP5K-SG48ITR FPGA Data sheet

#### 1.4 Board Overview

The VSDSquadron FPGA Mini (FM) board features the Lattice ICE40UP5K FPGA with the following capabilities:

- 48-lead QFN package

- 5.3K LUTs for flexible logic design

- 1Mb SPRAM and 120Kb DPRAM for efficient memory usage

- Onboard FTDI FT232H USB-to-SPI interface for programming and communication

- All 32 FPGA GPIO accessible for rapid prototyping

- Integrated 4MB SPI flash for configuration and data storage

- RGB LED for user-defined signaling

- Onboard 3.3V and 1.2V power regulators, with the ability to supply 3.3V externally

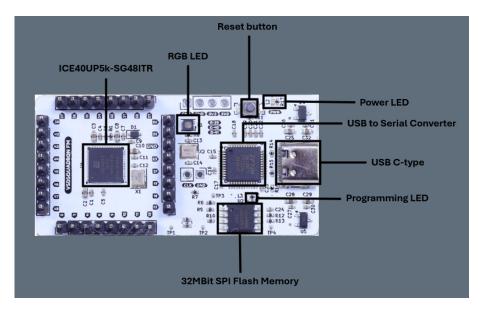

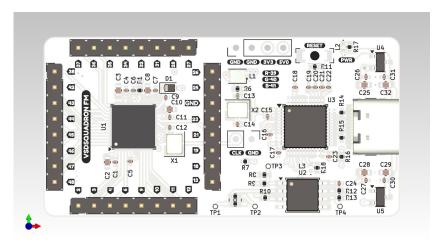

The following illustration in Figure 2 highlights various components of the VSDSquadron FPGA Mini (FM) board.

Figure 2: VSDSquadron FPGA Mini (FM) board

#### 1.4.1 Form Factor

The following are the dimensions of the VSDSquadron FPGA Mini (FM) board.

- $\bullet$  Form factor is 57.00 x 29.00 mm

- Maximum height of the component at the top side: 8mm

- Maximum height of the component at the bottom side: 1mm

| FNC              | Pin Type         | BANK | Differential Pair | Pin<br>number |

|------------------|------------------|------|-------------------|---------------|

| IOB_0a           | PIO              | 2    | -                 | 46            |

| IOB_2a           | DPIO             | 2    | TRUE_of_IOB_3b    | 47            |

| IOB_3b_G6        | DPIO/GBIN        | 2    | COMP_of_IOB_2a    | 44            |

| IOB_4a           | DPIO             | 2    | TRUE_of_IOB_5b    | 48            |

| IOB_5b           | DPIO             | 2    | COMP_of_IOB_4a    | 45            |

| IOB_6a           | PIO              | 2    | -                 | 2             |

| IOB_8a           | DPIO             | 2    | TRUE_of_IOB_9b    | 4             |

| IOB_9b           | DPIO             | 2    | COMP_of_IOB_8a    | 3             |

| IOB_10a          | DPIO             | 1    | TRUE_of_IOB_11b   | -             |

| IOB_11b_G5       | DPIO/GBIN        | 1    | COMP_of_IOB_10a   | _             |

| creset_b         | CONFIG           | 1    | _                 | 8             |

| IOB_12a_G4_CDONE | CONFIG/DPIO/GBIN | 1    | TRUE_of_IOB_13b   | -             |

| CDONE            | CONFIG           | 1    | -                 | 7             |

| IOB_13b          | DPIO             | 1    | COMP_of_IOB_12a   | 6             |

| IOB_16a          | PIO              | 1    | _                 | 9             |

| IOB_18a          | PIO              | 1    | _                 | 10            |

| IOB_20a          | PIO              | 1    | _                 | 11            |

| IOB_22a          | DPIO             | 1    | TRUE_of_IOB_23b   | 12            |

| IOB_23b          | DPIO             | 1    | COMP_of_IOB_22a   | 21            |

| IOB_24a          | DPIO             | 1    | TRUE_of_IOB_25b   | 13            |

| IOB_25b_G3       | DPIO/GBIN        | 1    | COMP_of_IOB_24a   | 20            |

| IOB_29b          | PIO              | 1    | -                 | 19            |

| IOB_31b          | PIO              | 1    | _                 | 18            |

| IOB_32a_SPI_SO   | DPIO/CONFIG_SPI  | 1    | _                 | 14            |

| IOB_33b_SPI_SI   | DPIO/CONFIG_SPI  | 1    | _                 | 17            |

| IOB_34a_SPI_SCK  | DPIO/CONFIG_SPI  | 1    | _                 | 15            |

| IOB_35b_SPI_SS   | DPIO/CONFIG_SPI  | 1    | _                 | 16            |

| VCCPLL           | VCCPLL           | -    | _                 | 29            |

| IOT_36b          | DPIO/I3C         | 0    | COMP_of_IOT_37a   | 25            |

| IOT-37a          | DPIO/I3C         | 0    | TRUE_of_IOT_36b   | 23            |

| IOT_38b          | DPIO             | 0    | COMP_of_IOT_39a   | 27            |

| IOT_39a          | DPIO             | 0    | TRUE_of_IOT_38b   | 26            |

| IOT-41a          | PIO              | 0    | -                 | 28            |

| IOT_42b          | DPIO             | 0    | COMP_of_IOT_43a   | 31            |

| IOT_43a          | DPIO             | 0    | TRUE_of_IOT_42b   | 32            |

| IOT_44b          | DPIO             | 0    | COMP_of_IOT_45a   | 34            |

| IOT_45a_G1       | DPIO/GBIN        | 0    | TRUE_of_IOT_44b   | 37            |

| IOT_46b_G0       | DPIO/GBIN        | 0    | -                 | 35            |

| IOT_47a          | PIO              | 0    | _                 | -             |

| IOT_48b          | DPIO             | 0    | COMP_of_IOT_49a   | 36            |

| IOT_49a          | DPIO             | 0    | TRUE_of_IOT_48b   | 43            |

| IOT_50b          | DPIO             | 0    | COMP_of_IOT_51a   | 38            |

| IOT_51a          | DPIO             | 0    | TRUE_of_IOT_50b   | 42            |

| RGB2             | LED              | 0    | _                 | 41            |

| RGB1             | LED              | 0    |                   | 40            |

| RGB0             | LED              | 0    | _                 | 39            |

| GND              | GND              | GND  | _                 | Paddle        |

| GND              | GND              | GND  | -                 | Paddle        |

| GND              | GND              | GND  | _                 | Paddle        |

| VCC              | VCC              | VCC  | -                 | 5             |

| VCC              | VCC              | VCC  | -                 | 30            |

| VCCIO_0          | VCCIO            | 0    | -                 | 33            |

| SPI_Vccio1       | VCCIO            | 1    | -                 | 22            |

| VCCIO-2          | VCCIO            | 2    | -                 | 1             |

| VPP_2V5          | VPP              | VPP  | -                 | 24            |

|                  | · - *            | ,    |                   |               |

Table 2: ICE40UP5K-SG48ITR FPGA device IO Bank Assignment

- 1.4.2 Table 2 shows ICE40UP5K-SG48ITR FPGA device IO Bank Assignment for communication Interfaces

- 1.4.3 The following table 3 lists the important components of the VSDSquadron FPGA Mini (FM) board

| Feature                     | ICE40UP5K-SG48ITR Specification            |

|-----------------------------|--------------------------------------------|

| Technology Node             | 40 nm                                      |

| Logic Cells                 | 5,280                                      |

| Flip-Flops                  | 4,960                                      |

| SRAM Blocks                 | 120 kbits                                  |

| DSP Blocks                  | None                                       |

| Package Type                | SG48                                       |

| I/O Pins                    | 39                                         |

| I/O Standards Supported     | LVCMOS, LVDS                               |

| Maximum Operating Frequency | 133 MHz                                    |

| Clock Sources               | Internal oscillator and external clock     |

| Core Voltage                | 1.2V                                       |

| I/O Voltage                 | 3.3V, 2.5V, 1.8V                           |

| Operating Temperature Range | -40°C to 85°C                              |

| Development Tools           | Project Icestorm, Yosys, and NextPNR tools |

Table 3: ICE40UP5K-SG48ITR FPGA Specifications

#### 1.5 Handling the Board

To avoid causing any damage or malfunctions, it is important to be mindful of the following points when handling or operating the board:

- To prevent any damage, make sure to handle the board while taking electrostatic discharge (ESD) precautions.

- Power down the board by disconnecting the board from USB port

#### 1.6 Operating Temperature

Designed for Room Temperature. The standard range for room temperature in Celsius is typically considered to be between 20 to 35 degrees Celsius (or 68 to 95 degrees Fahrenheit).

#### 1.7 Powering Up the Board

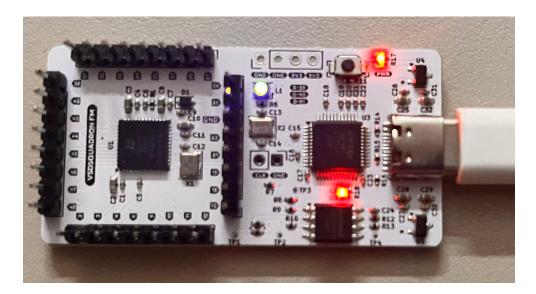

Connect the Type-C end of USB cable to the board as shown in Fig 3 and connect USB to PC. Refer to Installation and Settings for programming the board. Do this step after software installation, which is a time-consuming process

Figure 3: Micro-C end of USB cable connected to board

### 2 Installation and Settings

This section provides information about the software and hardware settings required to run "RGB blink LED" program on the VSDSquadron FPGA Mini (FM) board using Yosys, nextpnr and Project IceStorm

#### 2.1 Installation Instructions for Windows Users

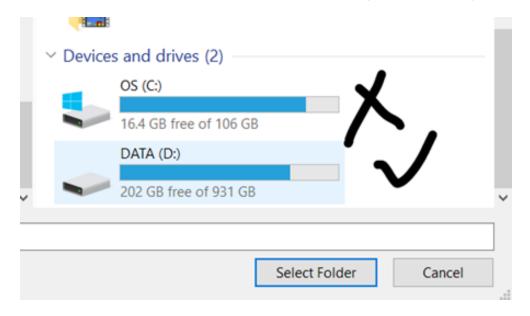

• Make sure your C drive or D drive has at least 100GB space (as shown in Fig 4)

Figure 4: Diskspace check

- Download VSDSquadron FPGA Mini (FM) Software on your laptop

- Unzip the downloaded file and follow the below instructions

- Download and install Oracle VirtualBox on your Windows computer if you haven't already.

You can download it from the official website

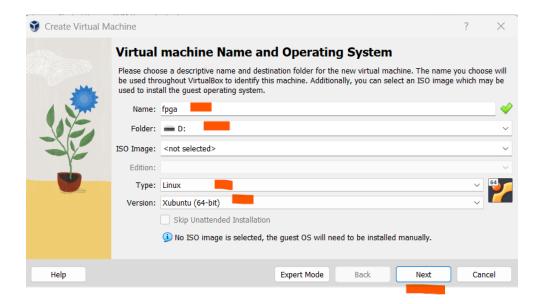

- Launch VirtualBox and click on the "New" button to create a new virtual machine. Fill up the details exactly as highlighted in RED as shown in the Fig 5.

- In the "Create Virtual Machine" wizard, enter a name for the virtual machine and select the operating system type as Linux and version as Xubuntu (64-bit) that matches the one installed in the VDI file you want to open. And then click on "Next"

Figure 5: Virtual Machine Launch

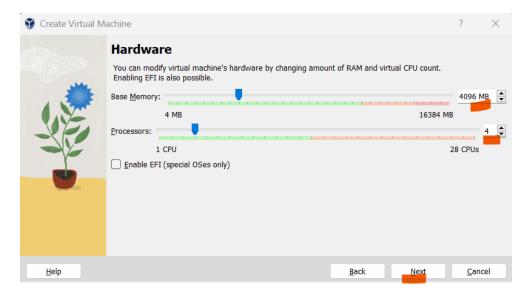

• On the next screen, allocate memory as 4GB (or 4096 MB) and number of CPUs as 4, as shown in Fig 6. Then click on "Next" button

Figure 6: Allocate RAM and Number of CPUs  $\,$

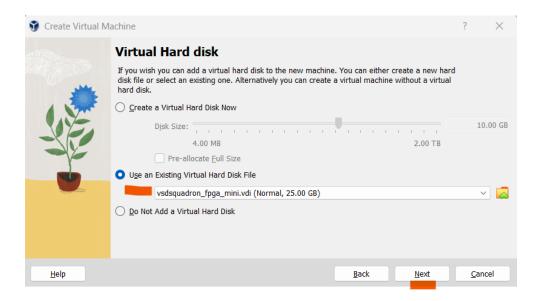

• Create a virtual hard disk. Choose the "Use an existing virtual hard disk file" option and click on the folder icon to browse to the location of the unzipped VDI file on your Windows computer as shown in Fig 7. Once done, click on "Next"

Figure 7: Choose VSDSquadron FPGA Mini VDI

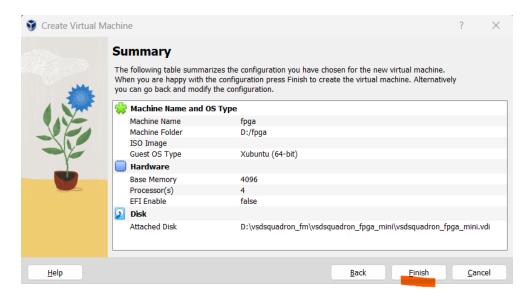

• Click on the "Finish" button as shown in Fig 8

Figure 8: Finish Setup

• Once the virtual machine is created, select it from the list of available virtual machines in the VirtualBox Manager and click on the "Start" button to launch it, as shown in Fig 9. It would take about 2-3 minutes to start the virtual machine

Figure 9: Start virtual machine

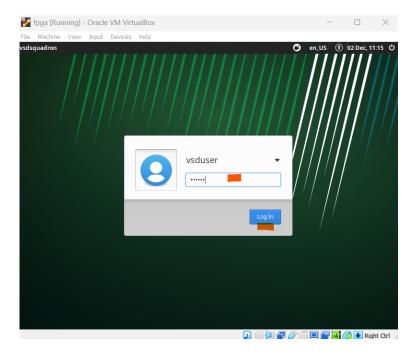

• The VM will start and prompt for password as shown in Fig 10. Enter the password as "vsdiat" and click on "Log In" button

Figure 10: Enter Password

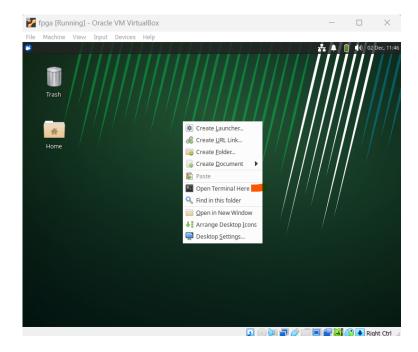

• You will see a window as shown in Fig 11. Take your cursor in the middle of the screen and right click on mouse. You will see lot of options as shown in same Fig 11. You need to left click on terminal as marked in RED in below Fig 11

Figure 11: Steps to Open Terminal

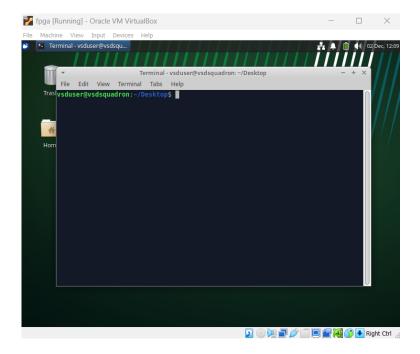

$\bullet\,$  You should see a terminal window as shown in below Fig 12

Figure 12: View Terminal

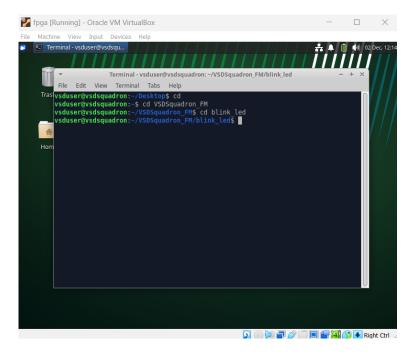

• Let's start our first project. To navigate through project directories in a UNIX environment, use the following commands:

```

cd

cd VSDSquadron_FM

cd blink_led

```

The commands above allow you to:

- Change to the home directory ('cd').

- Navigate to the 'VSDSquadron\_FM' folder, which has a sample project.

- Move into the 'blink\_led' directory, which is the first FPGA project to be tried on VSD-Squadron FPGA Mini (FM) board.

Refer to Fig 13 for more details

Figure 13: Navigate through project directory

- There is a preloaded project in "blink\_led" directory. To test the project on VSDSquadron FPGA Mini (FM) board, we need to make sure that the board is connected to the Oracle Virtual Machine. Perform below steps

- Connect the board to your PC, as shown earlier in Fig. 3.

- On the Virtual Machine, click on "Devices  $\to$  USB  $\to$  FTDI Single RS232-HS [J900]" as shown in Fig. 14.

Figure 14: Connecting the Board to USB

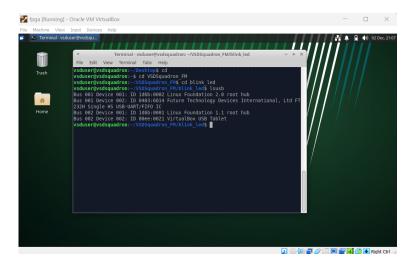

To confirm if the board is connected to the USB, type the 'lsusb' command in the terminal.

You should see a line stating "Future Technology Devices International," as shown in Fig. 15.

Figure 15: FTDI Message from 'lsusb' Command

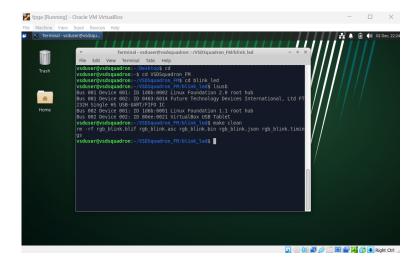

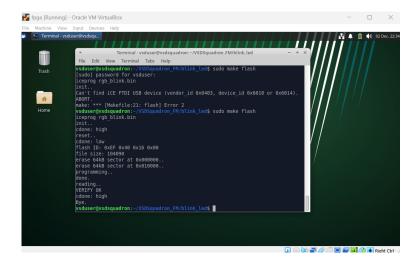

- $\bullet\,$  To program the VSDS quadron FPGA Mini (FM) board, follow these steps:

- Run the following command to clean up previous builds. Refer to Fig. 16:

make clean

Figure 16: Output Screen after 'make clean' command

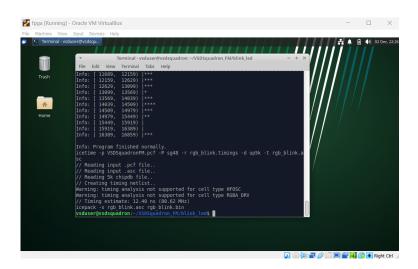

- Build the binaries for the FPGA board using below command. Fig. 17 shows the output screen after 'make build' command:

#### make build

Figure 17: Output Screen after 'make build' command

- Flash the code to the external SRAM with the following command:

#### sudo make flash

- After executing the above command, the screen will look as shown in Fig. 18.

Figure 18: Output Screen after Flashing the Code

- Note: If you get an error as shown in Fig. 18, then probably the board got disconnected. Try repeating the step as shown in Fig. 14

- Once the code is successfully flashed, you will see the RGB lights on the FPGA board blinking.

### 3 Board Component Placement

The following figure shows the placement of various components on the VSDSquadron FPGA Mini (FM) board.

#### 3.1 VSDSquadron FM top view

The following Figure 19 shows the top view of the VSDSquadron PRO RISC-V development board.

Figure 19: Silkscreen Top View

#### 3.2 VSDSquadron FM bottom view

The following Figure 20 shows the bottom view of the VSDSquadron FPGA Mini (FM) board silkscreen.

Figure 20: Silkscreen Top View

## 4 Revision History

The document's revision history provides a record of the alterations made to it, listed in chronological order, with the most recent revision first.

| Revision | Date | Description                |

|----------|------|----------------------------|

| 1.0      | -    | This is the first publica- |

|          |      | tion of this document      |

Table 4: Revision History

## 5 Help and support

- $\bullet$  Contact email ID vsd@vlsisystemdesign.com

- $\bullet$  Online Slack support https://vsdsquadron.slack.com/