# Open-source EDA community building using technology-mediated learning

Kunal Ghosh & Anagha Ghosh VLSI System Design

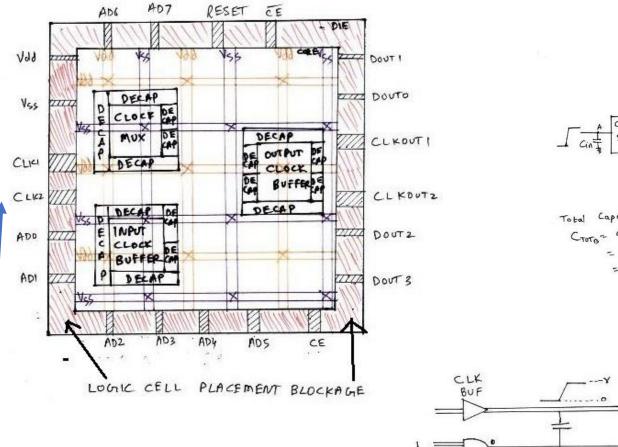

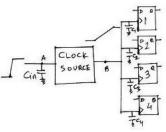

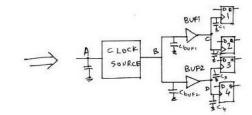

Total Capacitance at  $B \Rightarrow$   $C_{TOTB} = C_1 + C_2 + C_3 + C_4$  = 1 + 1 + 1 + 1 = 4F

Total Capacitance at B

CTOTS = CBUFI TCBUF2

- 1 + 1 = 2F

Total Capacitance at C

CTOTC = C1 + C2

- 1 + 1 - 2 F

Total Capacitance at D

Total Capacitance at D

Crots = Cs + C4

- 1 + 1 = 2F

CLOCK TREE SYNTHESIS

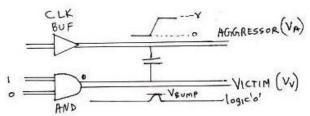

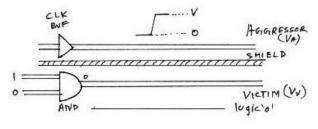

IF

$$V_{Bump} > V_{THRESHOLD}$$

$$V_V = \lfloor egic' i' \Rightarrow V'_V$$

No Bump Vv = logicial => 'o'v

→ NO FUNCTIONALITY CHANGE

OF AND GATE

⇒ COST ⇒ AREA INCREASE

PUE TO ADDITION

OF SHIELD

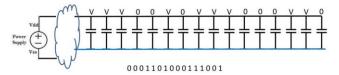

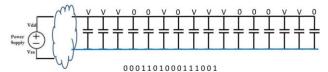

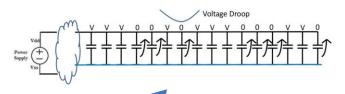

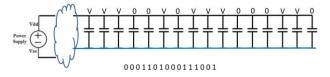

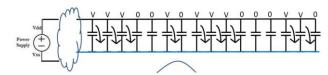

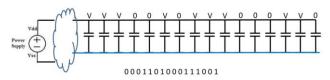

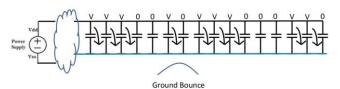

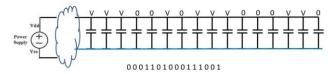

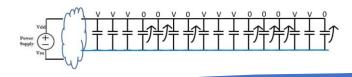

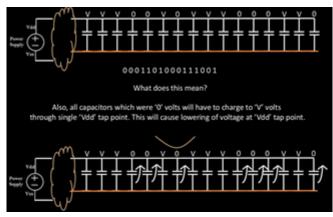

# Can you see voltage droop and ground bounce? — Infographics "An idea sketched to us by Srikanth Jadcherla"

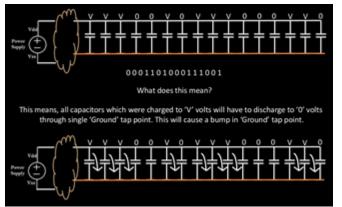

What does this mean?

This means, all capacitors which were charged to 'V' volts will have to discharge to '0' volts through single 'Ground' tap point. This will cause a bump in 'Ground' tap point.

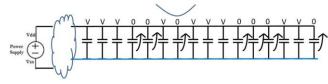

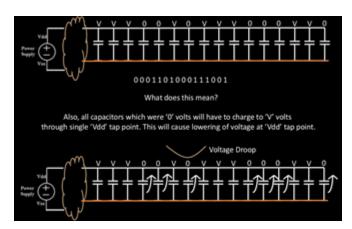

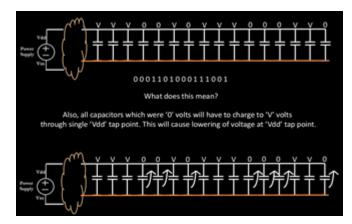

What does this mean?

Also, all capacitors which were '0' volts will have to charge to 'V' volts through single 'Vdd' tap point. This will cause lowering of voltage at 'Vdd' tap point.

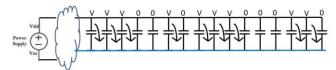

What does this mean?

This means, all capacitors which were charged to 'V' volts will have to discharge to '0' volts through single 'Ground' tap point. This will cause a bump in 'Ground' tap point.

What does this mean?

Also, all capacitors which were '0' volts will have to charge to 'V' volts through single 'Vdd' tap point. This will cause lowering of voltage at 'Vdd' tap point.

mdesigr

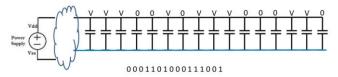

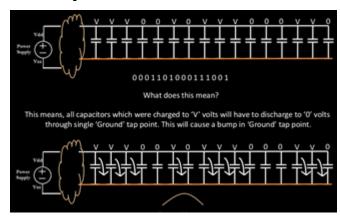

What does this mean?

This means, all capacitors which were charged to 'V' volts will have to discharge to '0' volts through single 'Ground' tap point. This will cause a bump in 'Ground' tap point.

What does this mean?

Also, all capacitors which were '0' volts will have to charge to 'V' volts through single 'Vdd' tap point. This will cause lowering of voltage at 'Vdd' tap point.

## Black board looked brighter than white

# "An idea seemed to be working with Khan Academy"

Srikanth Jadcherla Image2Infographics

# Launched 4 video courses, 2 FREE 2 PAID

**Promotional Announcements**

**Educational Announcements**

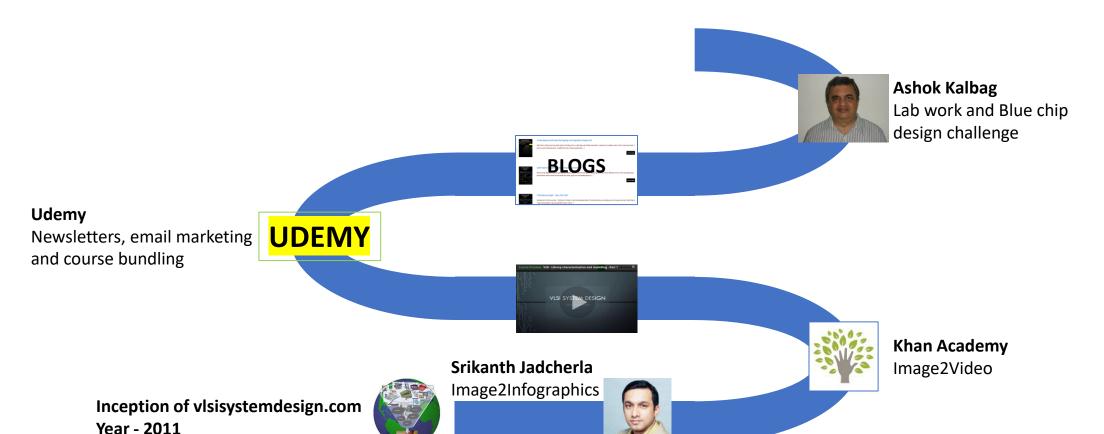

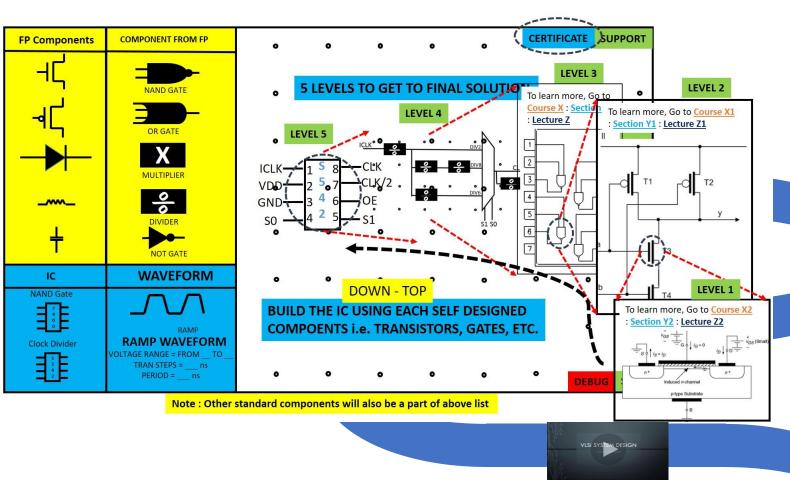

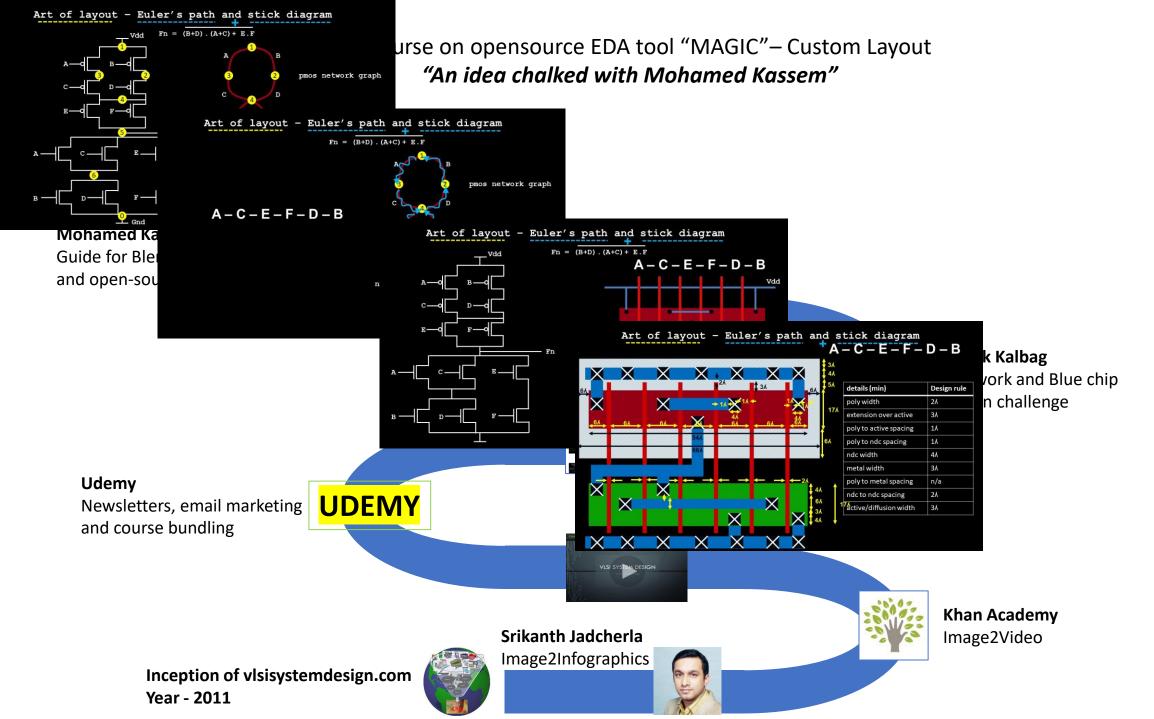

#### Udemy

Newsletters, email marketing and course bundling

Khan Academy Image2Video

Inception of vlsisystemdesign.com Year - 2011

## **Promotional Announcements**

#### **Educational Announcements**

#### Flipped classroom for VLSI & Semiconductors

"That's what we are being called by a Professor at IIT Bombay – Its really an honor"

Hi

I noticed you are looking for some real good alternative for classrooms where you can study and do labs while at home. So this mail might just be a useful one.

There are basically 3 primary reasons, you might just love the courses I built online -

You can study at your own pace. No hurry and no grading

You can put your queries forward in front of me as private message or in front of 13000 people who are already taking our courses. One of us will definitely get back to you in a day's time

You can download opensource EDA tools on your laptop, install them and learn from scratch. I have a course which explains how to download and install opensource EDA tools on your windows machine using Linux virtual box

Another really important reason why you might just choose the below courses on top of others, is its pricing. Month end is nearing, and I would like to offer up to 90% discount on all my courses. You might want to check out the links below before it expires in next 18hours

#### TCL Scripting -

New

and

https://www.udemy.com/vsd-tcl-programming-from-novice-to-expert/?couponCode=FLIPPED CLASSROOM

STA Webinar –

https://www.udemy.com/vsd-static-timing-analysis-sta-webinar/?couponCode=FLIPPED CLASSROOM

Library Characterization and modelling: Part 1 -

https://www.udemy.com/vlsi-academy-library-characterization-part-

/?couponCode=FLIPPFD\_CLA

## <u>2 promotional announcements</u> per month

**Promotional Announcements**

**Educational Announcements**

Newsletters, email marketing and course bundling

Khan Academy Image2Video

Inception of vlsisystemdesign.com Year - 2011

#### **Promotional Announcements**

#### **Educational Announcements**

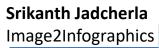

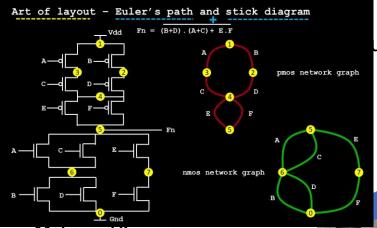

#### Let's unveil few more static power

Talking about leakage power or static power, one classic definition that comes into our minds is that of sub-threshold leakage current, which can be replicated or explained through below image

#### Tunneling current:

The explanation of tunneling current needs a knowledge on energy band diagrams of a MOS capacitor system as shown below:

# 4 educational announcements per month

### **Udemy**

Newsletters, email marketing and course bundling

So, in a MOS system, the metal gate and P-type silicon has fermi energy level, which are at different energy values. Now when 2 different systems with 2 different fermi levels are connected across SiO2, at thermal equilibrium when there are no currents flowing, the fermi-level of all the components attached are expected to be at same level, and while that process, the energy band of P-type silicon at the Oxide-

Inception of visisystemdesign.com Year - 2011

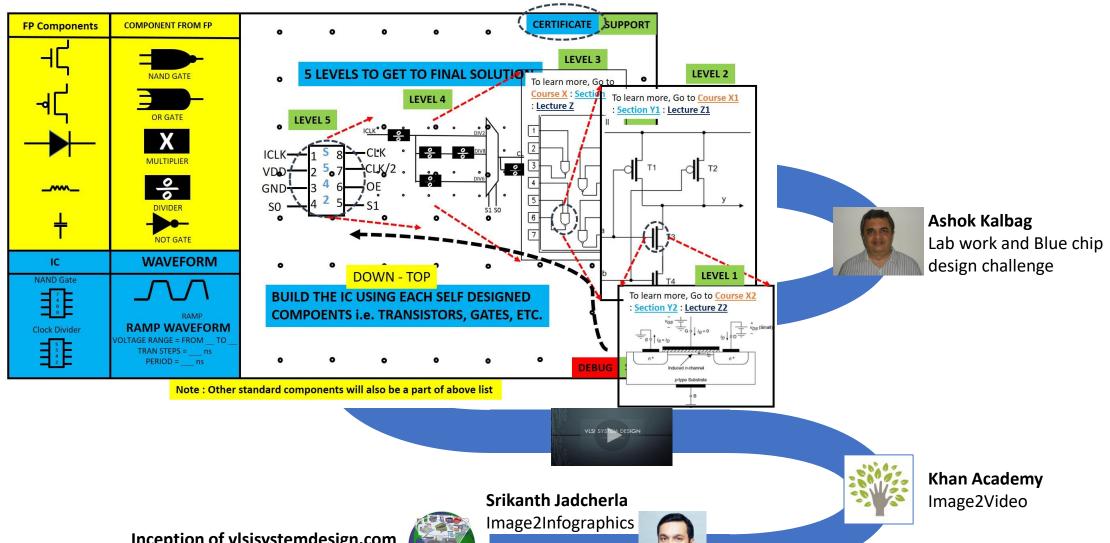

# Only course enrollment was not enough – course completion needed "A seed planted in our heads by Ashok Kalbag – Labs and Design challenge"

# Only course enrollment was not enough – course completion needed "A seed planted in our heads by Ashok Kalbag – Labs and Design challenge"

#### \*FP - FIRST PRINCIPLE

# Only course enrollment was not enough – course completion needed "A seed planted in our heads by Ashok Kalbag – Labs and Design challenge"

\*FP - FIRST PRINCIPLE

**Designed in 2015** Still work in progress Waiting to finish relevant courses

**Ashok Kalbag** Lab work and Blue chip design challenge

**Khan Academy** Image2Video

Image2Infographics

Year - 2011

# Only course enrollment was not enough – course completion needed "A seed planted in our heads by Ashok Kalbag – Labs and Design challenge"

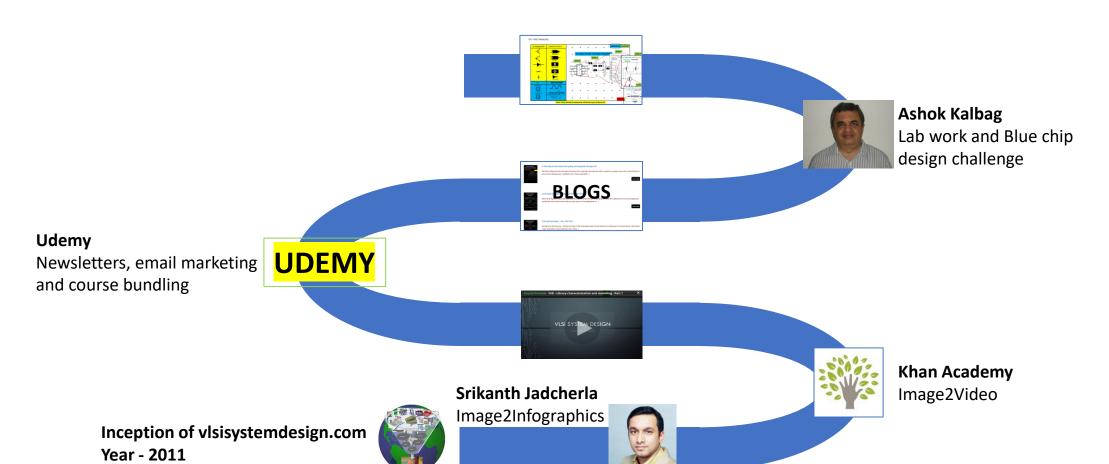

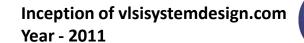

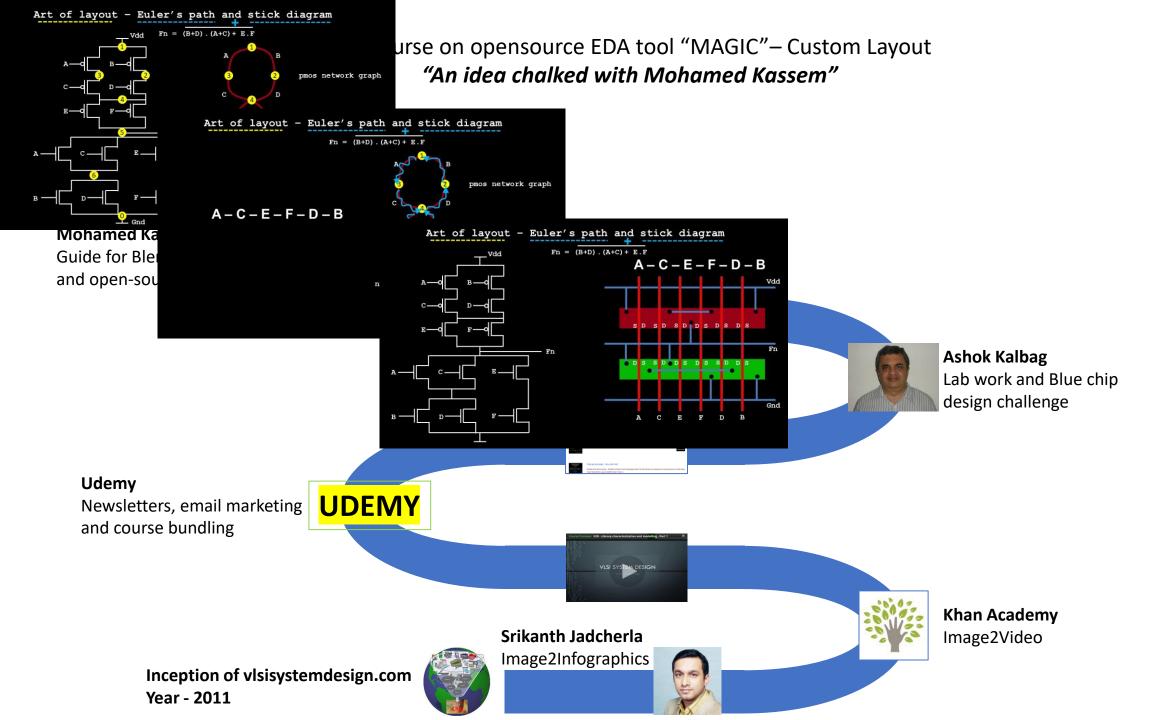

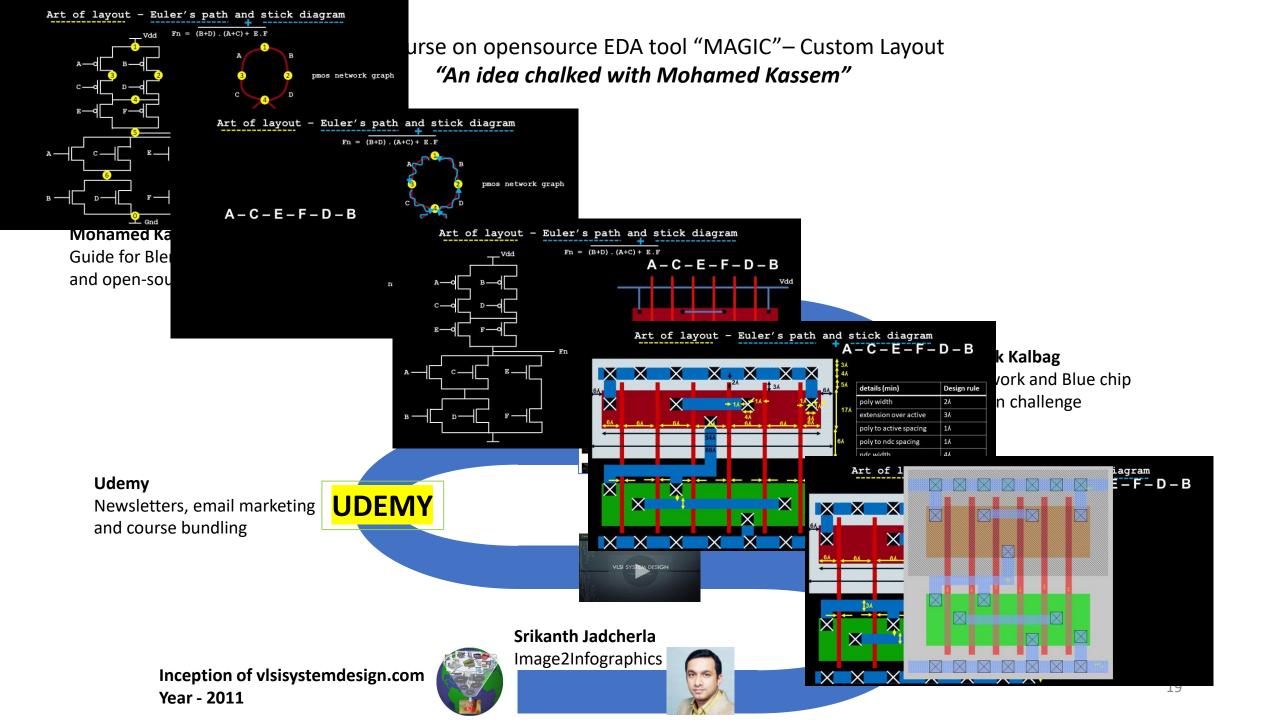

# First course on opensource EDA tool "MAGIC" – Custom Layout "An idea chalked with Mohamed Kassem"

#### **Mohamed Kassem**

Guide for Blended learning concept and open-source tool integration

Ashok Kalbag Lab work and Blue chip design challenge

#### Udemy

Newsletters, email marketing and course bundling

Srikanth Jadcherla Image2Infographics

Khan Academy Image2Video

Inception of vlsisystemdesign.com Year - 2011

urse on opensource EDA tool "MAGIC" – Custom Layout

"An idea chalked with Mohamed Kassem"

#### Mohamed Kassem

Guide for Blended learning concept and open-source tool integration

Ashok Kalbag

Lab work and Blue chip

design challenge

#### Udemy

Newsletters, email marketing and course bundling

# Srikanth Jadcherla

Image2Infographics

Khan Academy Image2Video

Inception of vlsisystemdesign.com Year - 2011

urse on opensource EDA tool "MAGIC" – Custom Layout

"An idea chalked with Mohamed Kassem"

Ashok Kalbag Lab work and Blue chip design challenge

#### **Udemy**

Newsletters, email marketing and course bundling

**BLOGS**

## Srikanth Jadcherla

Image2Infographics

# First course on opensource EDA tool "MAGIC" – Custom Layout "An idea chalked with Mohamed Kassem"

#### **Mohamed Kassem**

Guide for Blended learning concept and open-source tool integration

Ashok Kalbag Lab work and Blue chip design challenge

#### Udemy

Newsletters, email marketing and course bundling

# First course on opensource EDA tool "MAGIC" – Custom Layout

#### "An idea chalked with Mohamed Kassem"

# A complete guide to install opensource EDA tools

#### **Mohamed Kassem**

Guide for Blended learning concept and open-source tool integration

**Ashok Kalbag** Lab work and Blue chip design challenge

#### **Udemy**

Newsletters, email marketing and course bundling

# First course on opensource EDA tool "MAGIC" – Custom Layout "An idea chalked with Mohamed Kassem"

#### **Mohamed Kassem**

Guide for Blended learning concept and open-source tool integration

**Ashok Kalbag** Lab work and Blue chip design challenge

#### Udemy

Newsletters, email marketing and course bundling

Srikanth Jadcherla

# Innovators needs right tools at right price

**Tim Edwards**MAGIC and qflow support,

documentation and opensource mentor

**Mohamed Kassem**

Guide for Blended learning concept and open-source tool integration

Ashok Kalbag Lab work and Blue chip design challenge

Udemy

Newsletters, email marketing and course bundling

Srikanth Jadcherla Image2Infographics

Khan Academy Image2Video

## Innovators needs right tools at right price

## Acknowledgments

- Tim Edwards from opencircuitdesign.com

- Email-id tim@opencircuitdesign.com

And approximate and accompanies and accompanie

Ashok Kalbag

Lab work and Blue chip

design challenge

Ashok Kalbag

MAGIC and qflow support,

documentation and opensource mentor

**Tim Edwards**

Newsletters, email marketing and course bundling

Srikanth Jadcherla

Image2Infographics

## Innovators needs right tools at right price

#### Acknowledgments

- Tim Edwards from opencircuitdesign.com

- Email-id tim@opencircuitdesign.com

**Udemy**

and course bundling

Kunal Ghosh, Dig

off expert at VLS

\*\*\*\*

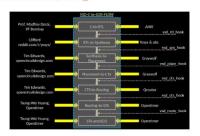

Figure 1: VSDFLOW framework

VSDFLOW is designed in such a flexible way, that user can pitch-in at any point of flow and some of them are enumerated below:

1. VSDFLOW hooks enables user to provide constraints in individual tool format or standard SDC format. Using this feature, user can switch to any tool within VSDFLOW framework. See figure 2

Figure 2: Different constraints format

in industries, and achieve desired results, there-by enabling user to focus on crafting the best requirements for design. See

#### **Tim Edwards** MAGIC and gflow support, documentation and opensource mentor

Instance Count

Table 1: openMSP430 (by opencores.org)

965um x 697um

9353

We have tested VSDFLOW with OSU 180nm technology and

below designs show the results in terms of performance and area

Results

PicoRV32 is a CPU core written by Clifford, that implements the RISC-V RV32IMC Instruction Set and available on github

| Synthesis           |                |

|---------------------|----------------|

| Runtime             | 1min           |

| Operating Frequency | 322MHz         |

| Instance Count      | 14828          |

| PNR                 |                |

| Runtime             | 1hr 20min      |

| Operating Frequency | 387MHz         |

| Area                | 1192um x 877um |

| Instance Count      | 14828          |

Table 2: picorv32 (by Clifford)

#### CORTEX-M0

An example system of MCU which contains a single cortex-m0

#### Conclusions

- VSDFLOW was shared with VSD community and 253 people sucessfully executed their designs with this flow

- · A beginners guide in form of video course is developed to assist for OPHW tool installation and enhanced the usage of VSDFLOW, which in turn is bringing out new ideas and de-

- · VSDFLOW has been tested and works seamlessly on designs upto 100k instance count, from opencores(for eg. open-MSP430) and industry(ARM, SiFive)

#### Forthcoming Research

- 1. For design size with more than 100k to 1.6M instance count, a hierarchical approach is under development

- 2. VSDFLOW is working towards to include post-layout timing results with back-annotated parasitics included

- 3. VSDFLOW is enabling an automated timing ECO framework, using ECO engine from Opentimer. Using this feature, user will be able to provide list of violating endpoints and VSDFLOW-ECO will return list of ECO fixes

#### Acknowledgements

Thanks to Tim Edwards, who has been continously helping in various aspects of qflow enablement within VSDFLOW.

VSDFLOW inception and making it available for community

• Thanks a lot to Tsung-Wei Huang for prompt response on any query relate to Opentimer, which has led to resolve many doubts and queries raised by community to VSD team. From community feedback, Tsung-Wei Huang plans to update Opentimer STA tool, which will support advanced timing

\*graywolf placement runtime reduction for designs with in-

Newsletters, email marketing **UDEMY**

Sr

#### **Tsung-Wei Huang**

Opentimer STA tool support and technical guidance

**Tim Edwards** MAGIC and qflow support, documentation and opensource mentor

#### **Mohamed Kassem**

Guide for Blended learning concept and open-source tool integration

**Ashok Kalbag** Lab work and Blue chip design challenge

Newsletters, email marketing and course bundling

Srikanth Jadcherla

Image2Infographics

Opentimer STA tool support and technical guidance

**Tim Edwards** MAGIC and qflow support, documentation and opensource mentor

Kunal Ghosh, Digital and Sign-

off expert at VLSI System ★★★★★ (53)

Types of setup/hold analysis

1. reg2reg 2. in2reg

3. reg2out

4. in2out 5. clock gating

#### Homework-

• Install Ubuntu virtual box if using windows

• After you install Ubuntu virtual box, install opentimer tool from below link

#### References:

Tsung-Wei Huang (twh760812@gmail.com) – owner of opentimer tool

# **Udemy**

Newsletters, email marketing and course bundling

# Srikanth Jadcherla

**Khan Academy** Image2Video

**Ashok Kalbag**

design challenge

Lab work and Blue chip

#### **Tsung-Wei Huang**

Opentimer STA tool support and technical guidance

#### Homework-

• Install Ubuntu virtual box if using windows

· After you install Ubuntu virtual box, install opentimer tool from below link

#### **Tim Edwards** MAGIC and qflow support, documentation and opensource mentor

#### References:

Tsung-Wei Huang (twh760812@gmail.com) - owner of opentimer tool

# **VSD - Static Timing Analysis -**

Kunal Ghosh, Digital and Signoff expert at VLSI System

Udemy

and course bundling

Types of setup/hold analysis

1. reg2reg 2. in2reg

3. reg2out

4. in2out 5. clock gating

6. recovery/removal

shown in below figure no. [1]

Figure 1: VSDFLOW framework

VSDFLOW is designed in such a flexible way, that user can pitch-in at any point of flow and some of them are enumerated below:

1. VSDFLOW hooks enables user to provide constraints in individual tool format or standard SDC format. Using this feature, user can switch to any tool within VSDFLOW framework. See figure 2

Figure 2: Different constraints format

# ttps://www.vlsisysteindesign.com

Sr

in industries, and achieve desired results, there-by enabling user to focus on crafting the best requirements for design. See

#### Results

We have tested VSDFLOW with OSU 180nm technology and below designs show the results in terms of performance and area

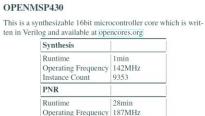

#### OPENMSP430

This is a synthesizable 16bit microcontroller core which is written in Verilog and available at opencores.org

| Synthesis           |               |

|---------------------|---------------|

| Runtime             | 1min          |

| Operating Frequency | 142MHz        |

| Instance Count      | 9353          |

| PNR                 |               |

| Runtime             | 28min         |

| Operating Frequency | 187MHz        |

| Area                | 965um x 697um |

| Instance Count      | 9353          |

Table 1: openMSP430 (by opencores.org)

#### PICORV32

PicoRV32 is a CPU core written by Clifford, that implements the RISC-V

| RV32IMC Instruction | l oct and available |

|---------------------|---------------------|

| Synthesis           |                     |

| Runtime             | 1 min               |

| Operating Frequency | 322MHz              |

| Instance Count      | 14828               |

| PNR                 |                     |

| Runtime             | 1hr 20min           |

| Operating Frequency | 387MHz              |

| Area                | 1192um x 877um      |

| Instance Count      | 14828               |

Table 2: picorv32 (by Clifford)

#### CORTEX-MO

An example system of MCU which contains a single cortex-m0

#### Conclusions

- VSDFLOW was shared with VSD community and 253 people sucessfully executed their designs with this flow

- · A beginners guide in form of video course is developed to assist for OPHW tool installation and enhanced the usage of VSDFLOW, which in turn is bringing out new ideas and de-

- · VSDFLOW has been tested and works seamlessly on designs upto 100k instance count, from opencores(for eg. open-MSP430) and industry(ARM, SiFive)

#### Forthcoming Research

- 1. For design size with more than 100k to 1.6M instance count, a hierarchical approach is under development

- 2. VSDFLOW is working towards to include post-layout timing results with back-annotated parasitics included

- 3. VSDFLOW is enabling an automated timing ECO framework, using ECO engine from Opentimer. Using this feature, user will be able to provide list of violating endpoints and VSDFLOW-ECO will return list of ECO fixes

#### Acknowledgements

. Thanks to Tim Edwards, who has been continously helping in various aspects of qflow enablement within VSDFLOW. Tim's continous and timely support has been really helpful in VSDFLOW inception and making it available for community

Thanks a lot to Tsung-Wei Huang for prompt response on any query relate to Opentimer, which has led to resolve many doubts and queries raised by community to VSD team. From community feedback, Tsung-Wei Huang plans to up-

date Opentimer STA tool, which will support advanced timing

\*graywolf placement runtime reduction for designs with in-

#### Inception of visisystemdesign.com Year - 2011

Newsletters, email marketing **UDEMY**

#### **Tsung-Wei Huang**

Opentimer STA tool support and technical guidance

**Tim Edwards** MAGIC and gflow support, documentation and opensource mentor

#### **Mohamed Kassem**

Udemy

Guide for Blended learnir and open-source tool inte

# Current Status

15 courses, 13000+ students across 126 countries

Lab work and Blue chip Recent Average Rating ? Total Students **3 Top Student Locations Countries With Students** India 47% 126 4.35 13,015 **United States** 28% 2% Egypt Newsletters, e **United Kingdom** 1% and course bu Canada 1%

Srikanth Jadcherla

Image2Infographics

# Journey has just begin...

#### **Tsung-Wei Huang**

Opentimer STA tool support and technical guidance

**Tim Edwards** MAGIC and qflow support, documentation and opensource mentor

#### **Mohamed Kassem**

Guide for Blended learning concept and open-source tool integration

**Ashok Kalbag** Lab work and Blue chip design challenge

Newsletters, email marketing and course bundling

Srikanth Jadcherla

Image2Infographics

# What next?

#### What next?

# Sign-up @ <a href="https://www.vlsisystemdesign.com/sign-up/">https://www.vlsisystemdesign.com/sign-up/</a> to know more ©

# **THANK YOU – ANY QUESTIONS?**