## 16-mask process

Looks complex. not anymore!!

Kunal Ghosh

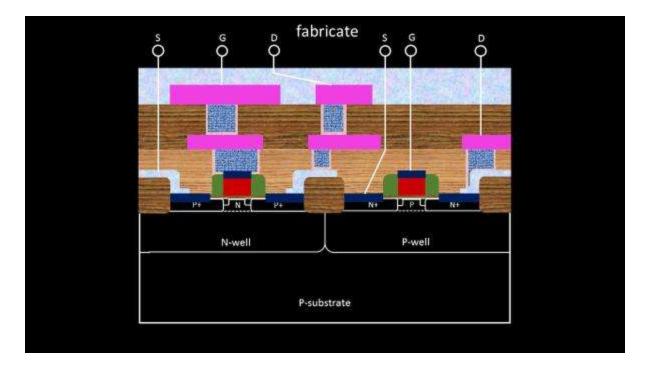

If you consider the above image, and wondering how complex it is to build and package a chip, you will change your opinion after the 16-masks that I would show in this and following blogs

Note: The 16-mask process is also covered in detail in my new course, for which the link is below:

https://www.udemy.com/vlsi-academy-custom-layout

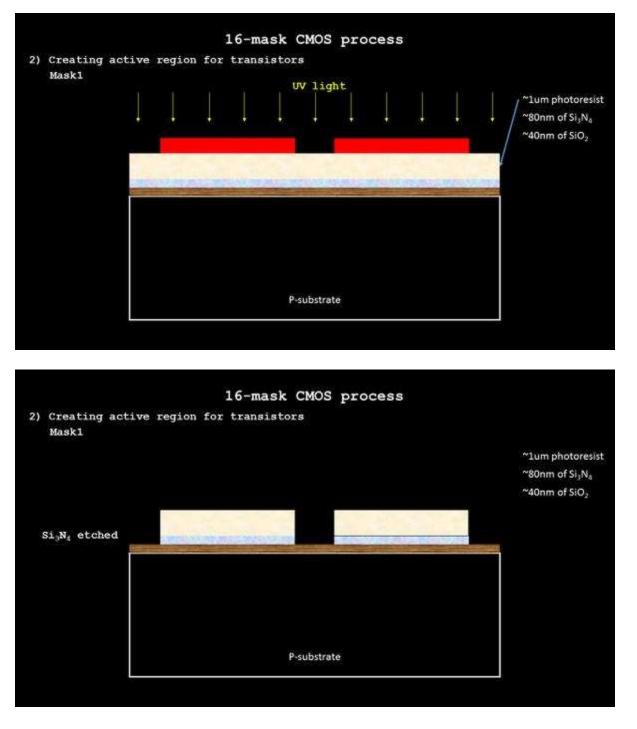

Let's skip some process steps and consider 1st mask below:

This is to create the active regions to build pmos/nmos transistors...will be evident as we move forward.

So, the mask is an opaque plate which blocks the UV light to react with certain areas of photo-resist. As shown above, part of resist is exposed to UV light, which gets washed away giving us the below open areas for further process steps, to etch away Si3N4:

Active regions are isolated from each other using isolation SiO2 (shown in below image), which is grown with 'LOCOS' technique (Local Oxidation of Silicon).

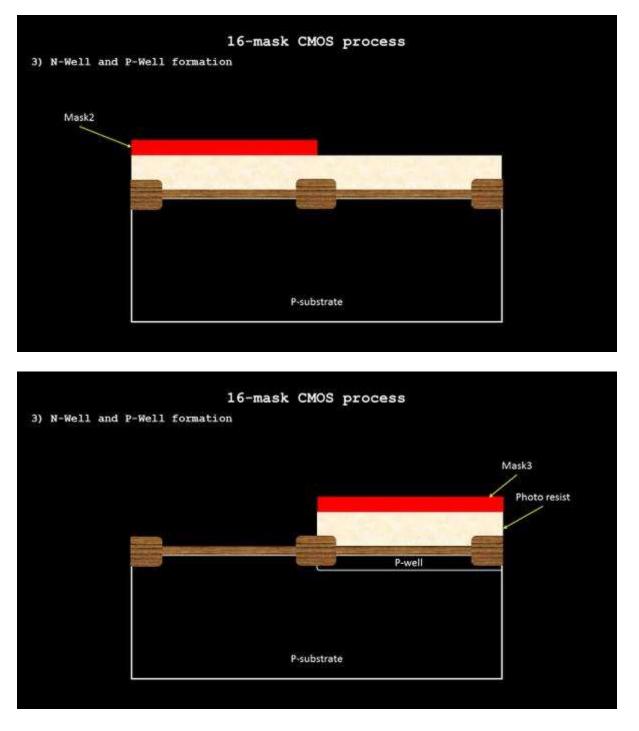

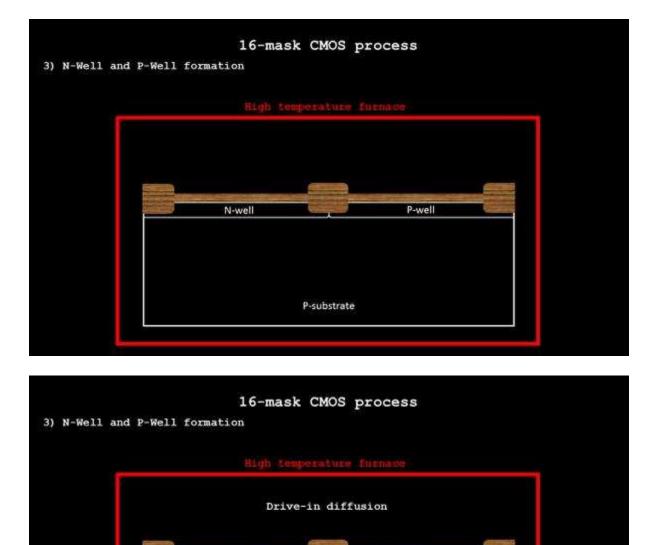

Mask2 and Mask3 will be used to create wells (nwell for pmos and pwell for nmos) as shown in below images:

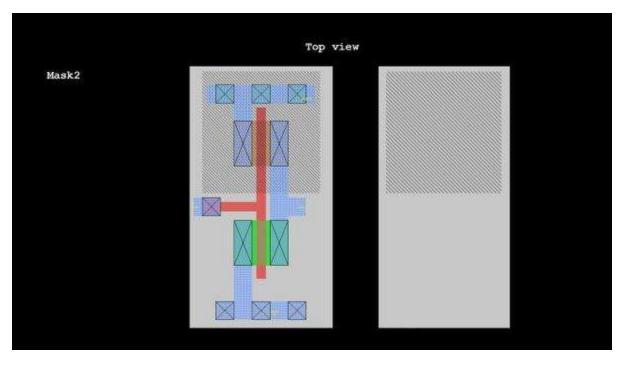

Now, if you want to relate a mask with layout, below image explains it all. Mask2 is nothing but the shaded nwell mask in a layout term

There is certain exchange of files that goes on between foundry and designers as a means of communicating design and process information. I will get back to this soon

Mask4 onwards is one where we create the most critical terminal of MOSFET i.e. gate terminal.

Once we have the nwell and pwell created, the entire structure is being placed in high temperature furnace and the 'wells are diffused into the substrate, as shown in below 2 images

|                         |                           | P-substrate        |                                    |                 |            |

|-------------------------|---------------------------|--------------------|------------------------------------|-----------------|------------|

| Ļ                       |                           |                    |                                    |                 |            |

| Next we fabric          | ate the most important    | t terminal of M(   | OS transistor i.e                  | . gate terminal | l          |

| Remember from           | m one of my 'Circuit o    | design and SPIC    | <u>E simulation</u> <sup>•</sup> c | ourse, I had ta | ilked abou |

| a a ma a income a matan | t manage atoms that's hal | Inful in tuning th | a the sale and scal                | taga Dalarri    |            |

P-well

N-well

ut some important parameters that's helpful in tuning the threshold voltage. Below image shows the same: It's the 'doping concentration' and 'oxide capacitance'

| Threshold Voltage Equation:                                           |                                                          |

|-----------------------------------------------------------------------|----------------------------------------------------------|

| $Vt = Vto + \gamma(\sqrt{ -2\Phi_f  + Vsb } \cdot \sqrt{ -2\Phi_f })$ |                                                          |

| Where                                                                 |                                                          |

| Vto = Threshold voltage at Vsb = 0, and is a f                        | function of                                              |

| manufacturing process                                                 |                                                          |

| $\gamma$ = body effect coefficient, expresses the in                  | npact of                                                 |

| changes in body bias Vsb (Unit is V <sup>0.5</sup> )                  |                                                          |

| $\Phi_f$ = Fermi Potential                                            |                                                          |

|                                                                       | 2 important terms for gate formation, as they control Vt |

| $\gamma = \frac{\sqrt{2qNA\varepsilon_{si}}}{c}$                      |                                                          |

|                                                                       |                                                          |

| = relative permittivity of silicon = 11.7                             |                                                          |

| N <sub>A</sub> + Roping concentration                                 |                                                          |

| q = charge of the electron                                            |                                                          |

| (C <sub>ox</sub> ) toxide capacitance                                 |                                                          |

| $\Phi_f = -\Phi_T * \ln \frac{N_a}{n_c}$                              |                                                          |

| <u>n</u> ,                                                            |                                                          |

| $n_i$ = intrinsic doping parameter for the subst                      | rate                                                     |

|                                                                       |                                                          |

|                                                                       |                                                          |

|                                                                       |                                                          |

Let's see how do we attain that. And here's mask4 that helps block nwell region and dope pwell with p-type impurity i.e. boron, as shown in below images:

|                                  |        | 16-mask | CMOS       | process |      |     |  |

|----------------------------------|--------|---------|------------|---------|------|-----|--|

| <ol> <li>Formation of</li> </ol> | 'gate' |         |            |         |      |     |  |

| Mask4                            |        |         |            |         |      |     |  |

|                                  | and a  |         |            |         |      | Cal |  |

|                                  |        |         |            |         |      |     |  |

| ī                                |        | N-well  |            | P-w     | vell |     |  |

|                                  |        |         | P-substrat | 1       |      |     |  |

| L                                |        |         |            |         |      |     |  |

| mation of 'gate' | 16-mask | CMOS process            |  |

|------------------|---------|-------------------------|--|

|                  |         |                         |  |

|                  |         |                         |  |

|                  | N-well  | P-well                  |  |

|                  |         | <sup>p</sup> -substrate |  |

Similarly, we dope nwell with n-type impurity i.e. Arsenic and use mask 5 for the same as shown in below images:

|                     | 16-mask CM | MOS process |       |

|---------------------|------------|-------------|-------|

| Formation of 'gate' |            |             |       |

|                     |            |             | Mask5 |

|                     |            |             |       |

|                     |            |             |       |

|                     |            |             |       |

|                     |            | P           |       |

|                     | N-well     | P-well      |       |

|                     |            | ,           |       |

|                     |            |             |       |

|                     | P-su       | bstrate     |       |

| 4) Formation | of 'ga | te' |     | 16-ma     | ask | CMOS     | pro | cess |      |   |  |

|--------------|--------|-----|-----|-----------|-----|----------|-----|------|------|---|--|

|              |        |     |     |           |     | Arseni   | ia  |      |      |   |  |

|              |        |     |     |           |     |          | 28  | 1    |      | - |  |

|              |        |     | N-v | N<br>vell |     | Ţ        |     | P-v  | vell |   |  |

|              |        |     |     |           | P   | -substra | te  |      |      |   |  |

The oxide present has been through lot of processes like n-type impurity doping, p-type impurity doping, nwell formation, pwell formation and so on, due to which its quality gets reduced. So, the original oxide is stripped off using HF acid and then re-grown to give high quality oxide, as shown in below image. This also helps in controlling oxide capacitance, a key parameter to control threshold voltage

| Formation of 'gat  | e'               |                   |                |        |

|--------------------|------------------|-------------------|----------------|--------|

|                    |                  |                   |                |        |

|                    |                  |                   |                |        |

| iginal oxide etche | d/etripped using | dilute budrot     | Duorio (HP) es | Jution |

| en re-grown again  |                  |                   |                | fueron |

|                    |                  |                   |                |        |

|                    |                  |                   |                |        |

|                    |                  | and in succession |                |        |

|                    | <u> </u>         |                   | p              |        |

|                    | ×                |                   | р              |        |

|                    | N-well           |                   | P-well         |        |

|                    | 1920 - Millio    |                   | P<br>P-well    |        |

|                    | 1920 - Millio    |                   | p<br>P-well    |        |

|                    | 1920 - Millio    | P-substrate       | P-well         |        |