Hello

It’s so robust… I can give you 4 instances of this

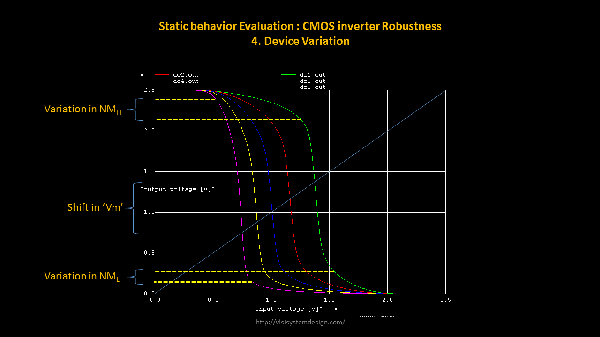

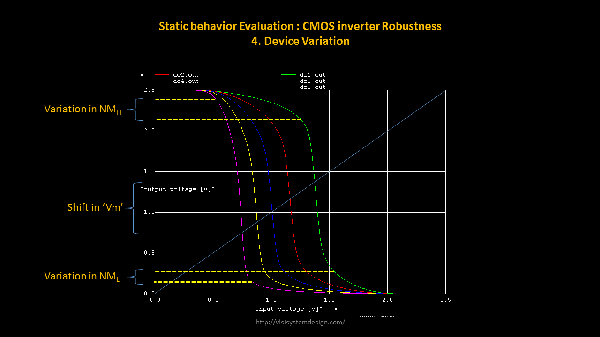

1) Vary PMOS width size to its maximum, keeping NMOS width constant and with couple of SPICE simulations, it reveals a minimal variation on ‘switching threshold (Vm)‘, while the functionality remains intact. Below 2 images has some SPICE simulations and numbers from experiments, I performed in my course “Circuit Design & SPICE simulations”

2) Vary PMOS width size to its maximum, keeping NMOS width constant and with couple of SPICE simulations, its also revealed that ‘noise margin‘ has hardly any variation, while functionality remains intact. Watch !!!

3) Vary power supply voltage (in full range, from slightly above threshold voltage till full supply VDD), keeping NMOS/PMOS width constant, the gain improves, while functionality is still intact. Watch !!

4) Now, vary, PMOS width from Max to Min, while vary NMOS width from Min to Max at same time, and there is very little impact in ‘switching threshold‘ and ‘noise margin‘, while functionality is still intact. Watch!!

“Remember, the storm is a good opportunity for the pine and the cypress to show their strength and stability” — Ho Chi Minh

So what is that storm, that will cause a CMOS logic to become unstable – may be a ‘glitch‘. I have given enough hint for you to figure out that. Well, that would one of the key topics of my next course, when I go for dynamic simulations.

Stay tuned !! Stay hungry !!

Happy Learning !!