Hello

Hope everyone had a good weekend :)!

And the reason for this post is to help friends and people in my circle to crack the interviews round the corner. I really apologize to people, if few of you are in midst of your vacation, and this important topic pops up as an update :(.

Don’t worry, you can read this later, as Linkedin will allocate few kilobytes on their server for this post 🙂

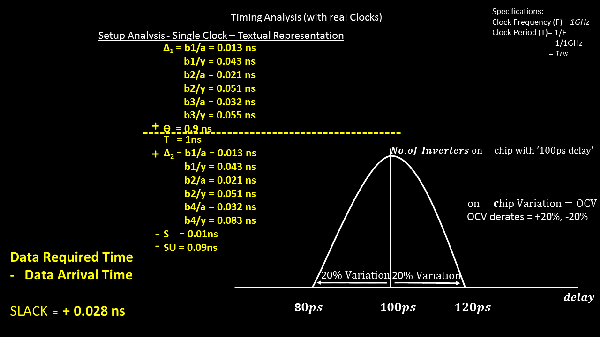

We will take up an OCV graph with +20% and -20% as derates (just to keep the calculations simple over here)

And we will use these OCV values (for now and usually its the case) on clock path only.

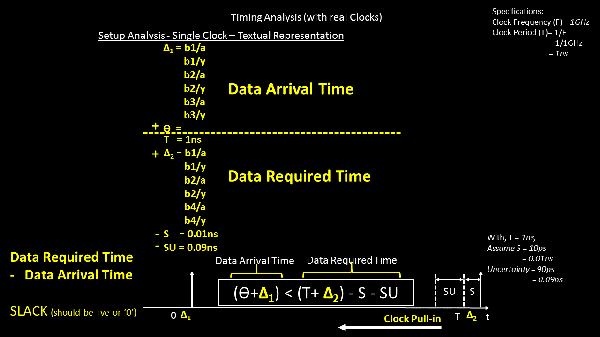

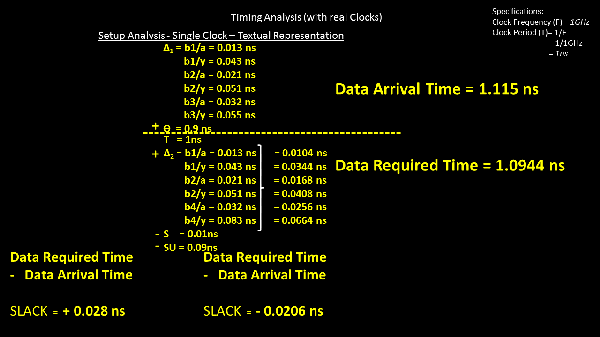

Now, for a moment, look back to the last post for SLACK calculation (for setup analysis). To make these OCV values really helpful for us, we need to pull-in the “data required time” and/or push-out the “data arrival time”.

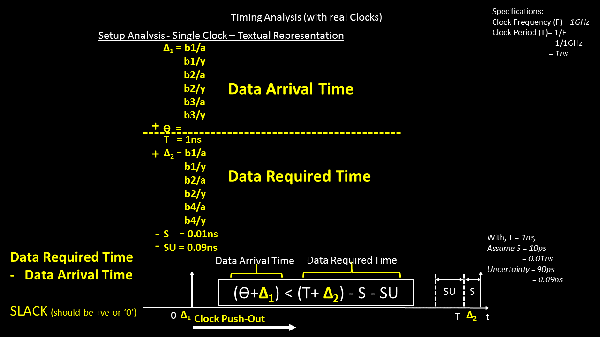

This will make a real worst-case analysis – meaning, if the SLACK meets the above criteria, we can guarantee you, the chip will function, no matter what.

By “pull-in”, we mean, we will bring the capture clock edge more towards the left hand side, as shown below (in the bottom-right of image), and ……. (sentence continued after below image)

…..(sentence continued from above), by the term “push-out”, we mean to push the launch clock, to the right side (as shown in bottom left of below image)

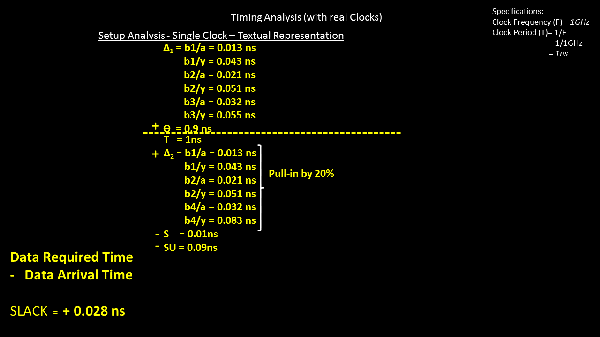

For now, lets do only one thing i.e pull-in the capture clock by 20%, i.e. every cell and net delay will be reduced by 20%. Below 2 images show the same

So, if (for eg.), delay of cell b1/y was 0.043ns, after applying OCV derates of 20%, the new delay of this cell will be 0.0344ns (no magic, I have used hand calculator :)), i,e, reduced delay of this cell from its original value by 20%

And how does this affects the “data required time” and “slack”….

OH MY GOD !!! (This is the real expression of an STA engineer, when he applies derates and sees the negative slack)

Yes, the slack is -20ps. This chip will fail... We have to run it with reduced frequency..We are not meeting specs… blah…blah..blah….. which “by-the-way” are true words of an STA engineer and his/her manager 🙂

And here enters an optimistic engineer, who follows exactly what “Joseph Sugarman” believes in that “Each problem has hidden in it an opportunity so powerful that it literally dwarfs the problem. The greatest success stories were created by people who recognized a problem a turned it into an opportunity”

Even the above problem has a “CATCH”, and the engineer who identifies this catch (in his team) will, probably, have his back ‘pat’ and receive ‘congratulations awards’ :).

Let me enable you guys for the same, in my next post 🙂

Thanks

Kunal