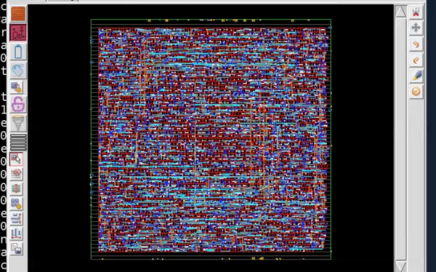

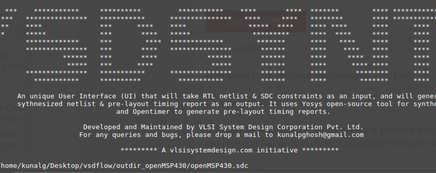

Facts – About below open-source EDA tool

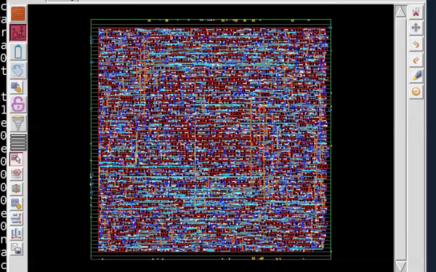

Why “integrated”? Because at lower nodes, you have to integrate other parts of the flow. Sign-off (you can see power and timing buttons below), clock tree synthesis (you can see synthesis button) must be integrated, so we have a fully integrated PnR flow that we built from day one.