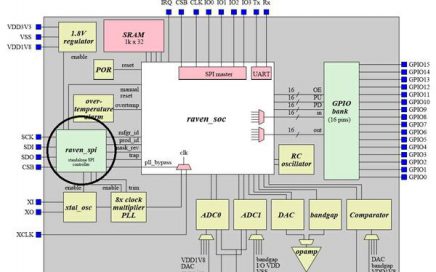

SPI model is a master/slave model. There’s some SPI master which determines who gets to transmit and who gets to receive. The output from SPI master is called MOSI (Master Out Slave In). If you have 2 slaves, slave 1 and slave 2, as shown below, MOSI goes to all the slaves .Then you have another line MISO (Master In Slave Out). All the wires are connected, as shown in below image. Then you have a master only function called SCLK, which goes to all the slaves. Now also, there must be a slave select (SS) for S1 and a slave select for S2.